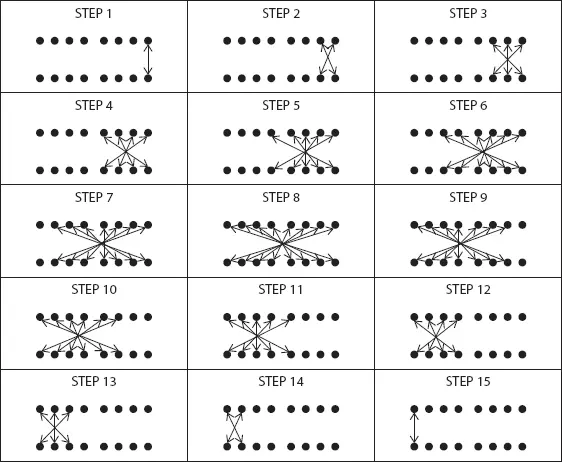

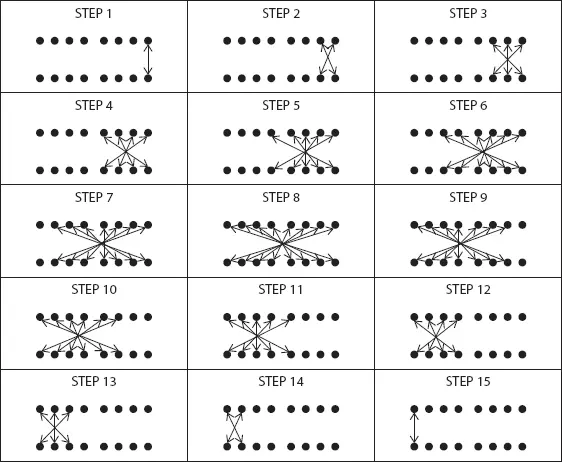

A Vedic sutra is a multiplication algorithm employed into the Vedic multiplier. These sutras were used to multiply decimal numbers traditionally; however, these sutras find application into multiplying binary and hexadecimal numbers equally. Urdhva Tiryakbhyam, Nikhimal sutram and Anurupyena sutras are the most preferred technique among the Vedic algorithm for reduction of delay, power and cell resources with a higher number of inputs [8–10]. Vedic multiplication is a fast method of calculation that provides unique techniques of calculation with half of simple rule and principle.

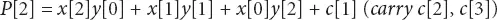

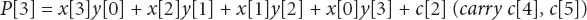

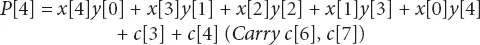

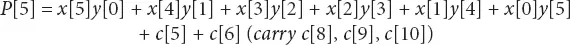

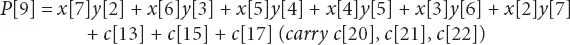

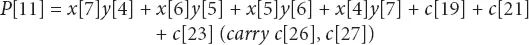

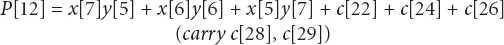

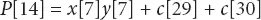

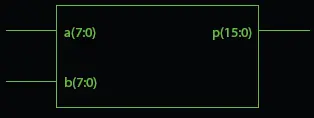

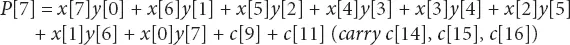

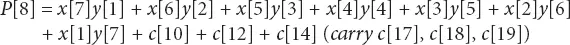

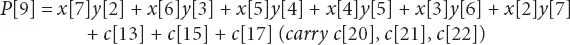

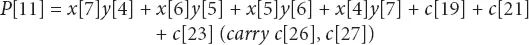

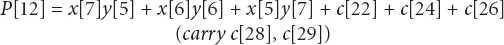

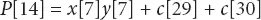

Here we have implemented multiplication of 8-bit number X[7:0] and Y[7:0]. Here X[0] presents the least significant bits (LSB), X[7] is the most significant bits (MSB), generate product P[15:0]. Each partial product P[0] to P[15] is calculated from equation given below. Equation ( 2.1) to ( 2.15) present the partial product P[0] to P[15], which is calculated in the internal multiplication algorithm. Which in turn produces the final product shown in equation ( 2.16). Internal carry bit created during computation given in as c[1] to c[30]. Carry bits made for P[14] and P[15] are neglected, because of the superfluous. Multiplication implemented with the addition of internal signals on each stage. Partial product P1-P15 shown the internal carry generation, which propagated to the next steps. Product P2-P15 requires additional hardware to add 4 bits since full adders can add only 3 bits. The addition of higher input performed using compressors with compressor architectural addition of more than three inputs implemented with reduced architecture and improved speed [11].

Figure 2.1 Multiplication of two 8-bit number with Urdhwa-Tiryakbhyam Sutra [28].

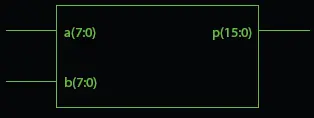

2.3 The Architecture of 8x8 Vedic Multiplier (VM)

The hardware architecture of 8x8 multiplier explained below is dependent on Urdhva-Tiryagbhyam. The advantages of VM algorithms found as generation of partial product and performed synchronously. It enhanced the parallel processing and preferred for the implementation of the binary multiplier. An 8x8 Vedic multiplication block diagram, presented in Figure 2.2implemented as a binary equation is given below. Each stage generates partial product, term as carrying. This carry input added with the next step of a partial product. Here requires adder can accept multiple data together. A full adder is a basic unit that can provide three data together. A compressor derived from the adder used to implement numerous inputs [12–16]. A 4:3 compressor accepts four inputs and maps the result into three output signals. 8x8 VM hardware architecture requires adding 20 input bits together, which is implemented with 20:5 compressor.

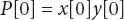

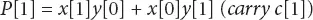

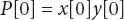

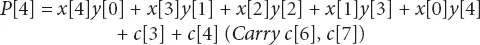

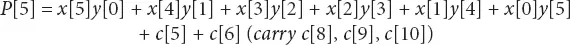

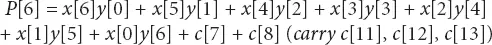

(2.1)

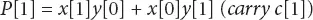

(2.2)

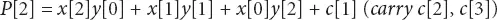

(2.3)

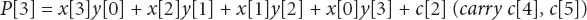

(2.4)

(2.5)

(2.6)

(2.7)

Figure 2.2 Block diagram of 8*8 multiplier.

(2.8)

(2.9)

(2.10)

(2.11)

(2.12)

(2.13)

(2.14)

(2.15)

(2.16)

2.3.1 Compressor Architecture

The combinational block requires to implement the more multiple are logical AND, OR, XOR. To perform addition half adder and full adder are preferred. The compressor can perform the addition of the higher number of inputs; the compressor focused. The compressor is made up of an adder block. The compressor maps a piece of higher information to lower the number of outputs with summation operation. A full adder is basic 3:2 compressor units of 3:2. It accepts three numbers of input and map as a sum and carries at the output terminal.

Figure 2.3 Compressor 3:2.

In Figure 2.3, the compressor is made of two XOR gates and a MUX Gate and by which we obtain the outputs as the sum and carry. The working principle of 3:2 compressor is similar to full adder, but delay, power, and time of 3:2 compressor is much lower than that of a full adder.

In Figure 2.4the compressor is made of three half adders and one full adder by which we obtain the outputs as the sum and two carries. The working principle of 4:3 compressor is to understand as two of the inputs applied to the half adder (H1), and the other two inputs are applied half adder (H2). The sum of two half adders given to (H3) half adder and the sum which obtained from (H3) is the sum of the compressor, and the carry which derived from all the half adders inputted to full adder. Sum and carry output of this full adder is named as SUM2 and carry is SUM3.

In Figure 2.55:3 a compressor is shown which is composed of two full adder (F1 & F2) and one-half adder. The working principle of this 5:3 compressor understood as, out of five three are the input to the full adder (F1). Sum output obtained from this full adder and the other two inputs applied to another full adder (F2).

Читать дальше