1 ...7 8 9 11 12 13 ...20

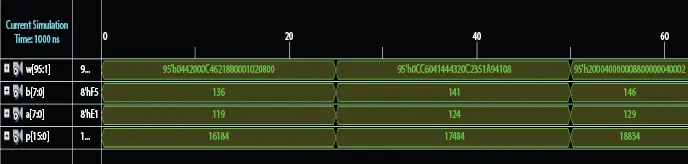

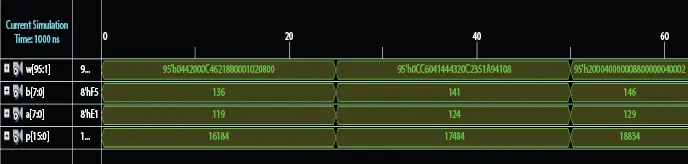

Figure 2.11 Behavioral simulation of 8x8 VM.

Figure 2.11presents the simulated waveform of which obtained while we implemented the 8x8 Vedic Multiplier. We have given input for a specific time, and it goes to the end till which we have mentioned stop in the test bench. Here a is 8-bit input and b is 8-bit input, and we are getting 16 bit as output, and it is represented in p. The multiplier is implemented with Verilog HDL using the Xilinx ISE tool. The synthesis result obtained from vertex-4 FPGA. An 8-bit VM requires 418 slices, 729 LUT and 67 IOB shown in Table 2.2. A similar effect is verified with cadence NCSIM and the implementation result confirmed with RTL compiler at gpdk 180nm technology. The simulation result shows that

Table 2.2 FPGA utilization summary report.

| Device utilization summary |

| Logic utilizations |

Used |

Available |

Utilization |

| Slices |

418 |

1672 |

4% |

| 4 input LUTs |

729 |

17344 |

4% |

| Bounded IOBs |

67 |

250 |

26% |

The case I Input A=8’d136 and B=8’d119 result in multiplier values p=16’h16184.

Case II Input A=8’d141 and B=8’d124 result in multiplier values p=16’h17484.

Case III Input A=8’d145 and B=8’d129 result in multiplier values p=16’h18834.

2.4 Results and Discussion

The performance parameter of 8-bit VM is judged by power consumption, delay, and area report obtained by the cadence RTL compiler. Completed implementation of an 8-bit Vedic multiplier is through the combinatorial block. The usage of the compressor reduces the requirement of resources. As the number of the logic gate but increases the interconnecting wires. Similarly, area requirements to interface multiple compressors significantly enhance the area and delay. In this section area, power and delay are presented due to logical resources and wires.

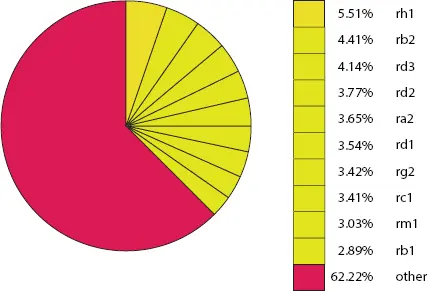

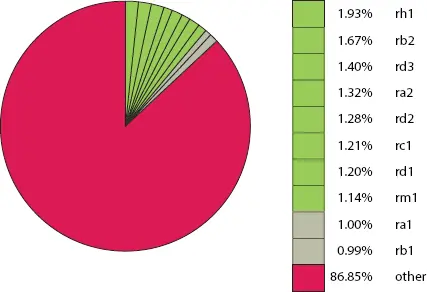

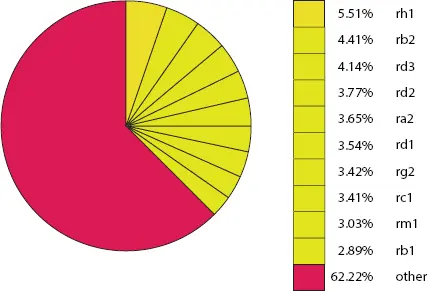

This pie chart in Figure 2.12presents the instance power used in the 8x8 Vedic Multiplier. In this chart, g1 and g2 determine compressor 10to4 and its usage of instance power is 15.79%. z1 and z2 define compressor 8to4, and its usage of instance power is 12.93%. d1 and d2 limit compressor 9to4 and its usage of instance power is 14.29%. N1 and N2 is a compressor of 7to3 whose power consumption is 8.19% of total power. M1 represents compressor 6to3, and its usage of instance power is 4.02%. V2 defines compressor 5to3, and its usage of instance power is 2.33%. Remaining all other compressors like t1 represents compressor 4to3, v1 represents compressor 5to3 and h1 defines about compressor 3to2 usage of instance power is 40.48%. An 8-bit Vedic more multiple logical blocks consume only 59.52% of total power. 40.48% of total power is consumed by another factor. The similar power distribution of the 16-bit multiplier is presented in Figure 2.13. Compressor block requires 37.78% of total power which 62.22% of total power consumed by other factors like wire.

Figure 2.12 Instance power usage of 8X8 vedic multiplier.

Figure 2.13 Instance power usage of 16X16 VM.

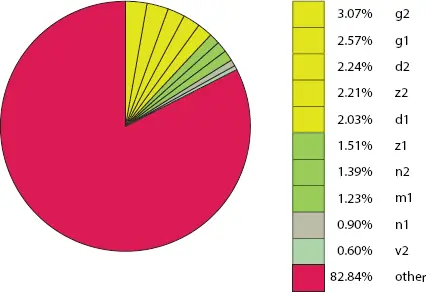

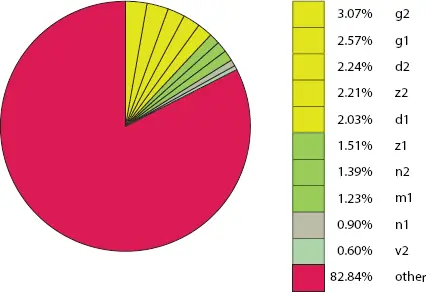

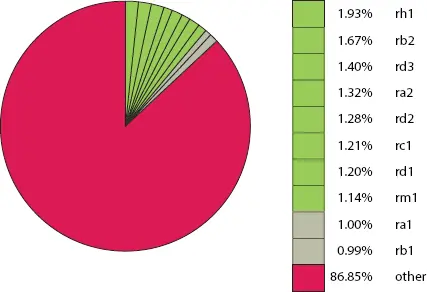

This pie chart in Figure 2.14defines the Net power used in the 8x8 Vedic Multiplier. The identification of the power-hungry block is identified from this chart. In this chart, g1 and g2 determine compressor 10to4; consumes 5.64% of the total net power. z1 and z2 define compressor 8to4, and its usage of net power is 3.72%. d1 and d2 define compressor 9to4, and its usage of net power is 4.27%. n1 and n2 define compressor 7to3, and its usage of net power is 2.29%. m1 defines compressor 6to3, and its usage of net power is 1.23%. v2 defines compressor 5to3, and its usage of net power is 0.60%. Remaining all other compressors like t1 denotes about compressor 4to3, v1 represents compressor 5to3 and h1defines about compressor 3to2 usage of net power is 82.24%. This pie chart in Figure 2.15defines the Net power distribution in the 16-bit multiplier.

Figure 2.14 Net power usage of 8X8 VM.

Figure 2.15 Net power usage of 16X16 VM.

Table 2.3presents the cell area requirement of the 8x8 Vedic Multiplier. Cell area report models the number of the basic cell requires to the design. To implement this project 139 cells are required, and the area which is obtained by cells is 1517, and the net area is “zero”. The total area which is accomplished is 1517, and there is no Wire Load for this Vedic Multiplier.

Table 2.3 Cell area of 8x8 vedic multiplier.

| Instance |

Cells |

Cell area |

Net area |

Total area |

Wire load |

| Vedic Multiplier |

139 |

1517 |

0 |

1517 |

(D) |

Table 2.4 Power constraints of 8x8 vedic multiplier.

| Instance |

Cells |

Leakage power(nW) |

Dynamic power(nW) |

Total power(nW) |

| vedicmultiplier |

139 |

13442.07 |

86424.01 |

99866.08 |

Table 2.5 Time constraint of 8x8 vedic multiplier.

| Pins |

Type |

Fan out |

Load (fF) |

Slew (ps) |

Delay (ps) |

Arrival (ps) |

| p[14] |

out port |

|

|

|

0 |

2637 R |

An instance of an 8-bit VM named Vedic multiplier requires 139 cells in this project; there is an unwanted sub-threshold current which is leakage of power in 13422.07nW (Nano Watt). Dynamic power, a part of power that consumed while the inputs are active, obtained value is 86424.01 nW and the total power which is obtained for this 8x8 Vedic Multiplier is 99866.08 nW shown in Table 2.4.

Here pin p[14] defines that it is the last output pin of 8x8 Vedic Multiplier and type defines whether it is input port or output port. The longest path arrival time (AT) of signal is calculated as the latency for a signal to arrive at point of consideration, for this project is 2637 ps shown in Table 2.5.

The 16x16 Vedic Multiplier requires 666 cells to implement this project, and the area which is obtained by cells is 5967, and the net area is “zero” as shown in Table 2.6. The total area in which it is accomplished is 5967, and there is no wire load for this Vedic Multiplier.

Читать дальше