2

Towards Tbit/s Wireless Communication Baseband Processing: When Shannon meets Moore

Matthias HERRMANN and Norbert WEHN

Microelectronic Systems Design Research Group, TU Kaiserslautern, Germany

Mobile communication plays a central role in our information society and is a key enabler in our connected world. The newest standard, 5G, features data rates >10 Gbit/s. Beyond 5G, data rates towards 1 Tbit/s are expected. The tremendous improvement in mobile communication has to be considered alongside the progress in the microelectronic industry. For many decades, improvement in silicon process technology provided better performance, lower cost per gate, higher integration density and lower power consumption. However, we have reached a point where Moore’s law is slowing down and microelectronics cannot keep up with the increased requirements coming from communication systems. Thus, the design of communication systems is no longer just a matter of spectral efficiency or bit/frame error rate. When it comes to implementation, design of communication systems requires a cross-layer approach covering information theory, algorithms, parallel hardware architectures and semiconductor technology to achieve excellent communications performance and high implementation efficiency. In this chapter, we focus on channel coding, which is a major source of complexity in digital baseband processing, and will highlight implementation challenges for the most advanced channel coding techniques, i.e. Turbo codes, Low Density Parity Check (LDPC) codes and Polar codes, for throughput requirements towards 1 Tbit/s.

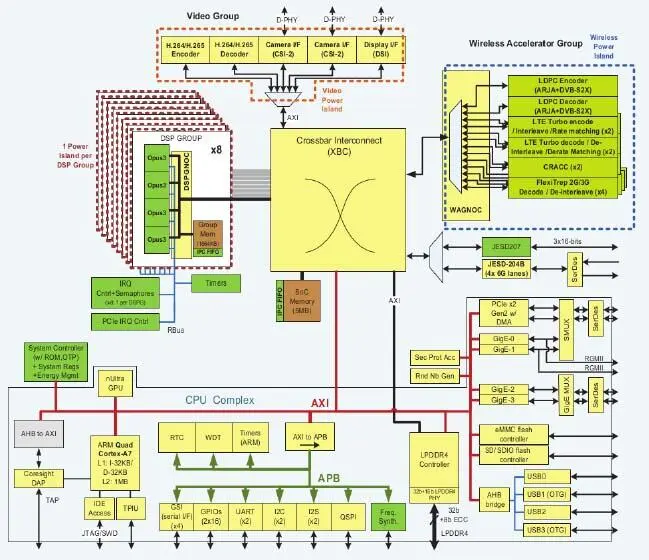

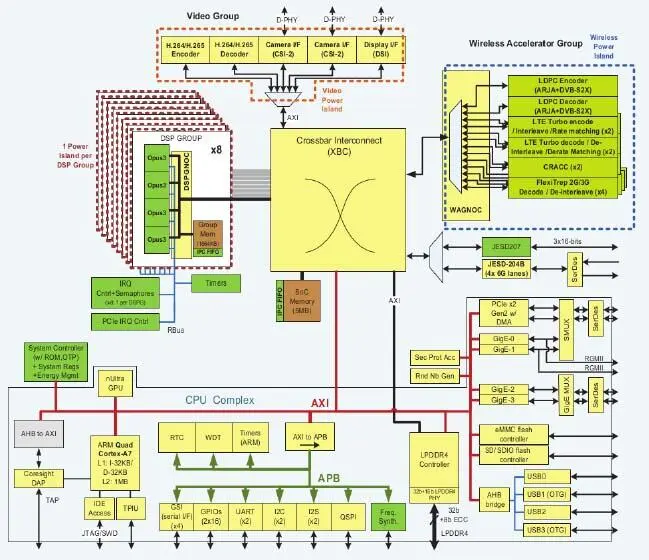

Wireless communication plays a central role in our information society and is a key enabler for our connected world. Today we already have more than 20 billion connected devices, and the majority of them are wirelessly connected. The first generation of mobile communication systems has shifted the communication from landline to handheld devices, followed by the third (3G) and fourth generations (4G) that marked the advent of the mobile internet. We have seen a tremendous increase in data rates over the different generations, for example, the Global System for Mobile Communications (GSM) featured about 10 kbps, the Universal Mobile Telecommunications System (UMTS) about 2 Mbit/s and Long Term Evolution Advanced (LTE-A) about 1 Gbit/s. The newest standard, 5G, features data rates > 10 Gbit/s. Beyond 5G, data rates toward 1 Tbit/s are expected (EPIC 2020). However, increasing data rates are not the only driver. With the advent of 5G, wireless communication is finding its way into a variety of applications with largely diverse requirements. Massive Internet of Things (IoT) demands for extremely low power, massive content applications (e.g. video streaming, cloud office) call for very high throughput and the use of wireless communication in control applications (e.g. autonomous driving, remote control, tactile internet) requires very fast response times in the order of 1 ms. Thus, communication has to support a huge throughput–latency range (5 orders of magnitude in throughput, 3 orders of magnitude in latency) and a large diversity of applications with different Bit Error Rate (BER)/Frame Error Rate (FER) requirements (Fettweis and Matus 2017). In this chapter, we focus on the digital baseband processing part of wireless communication. The main tasks of baseband processing are signal detection, parameter estimation, demodulation and channel decoding. Figure 2.1 shows a state-of-the-art commercial advanced baseband System-on-Chip (SoC) from the company Octasic ( http://www.octasic.com ). This SoC supports a wide range of communication standards from 2G to 5G. Assisting different standards demands for flexibility; on the other hand, power and energy efficiency requires dedicated optimized accelerators that demand a careful flexibility/implementation efficiency trade-off. A specialized hardware is 2 to 3 orders of magnitude more efficient than processor-based solutions that offer largest flexibility (Horowitz 2014). Hence, the SoC features a heterogeneous architecture composed of standard CPUs such as ARM cores, highly optimized low-power Digital Signal Processor (DSP) cores and dedicated accelerators.

The most computational-intensive part in baseband processing is channel decoding. Channel coding is an essential part in any communication system to guarantee reliable transmission, and enables the correction of errors that are induced during data transmission over noisy channels. It has a long history, going back to Shannon’s famous channel coding theorem in 1948 (Shannon 1948), and is based on the solid theoretical mathematical framework of information theory. Coding evolved as a very active research field and achieved a major breakthrough in 1993, when Claude Berrou wondered whether two small convolutional codes arranged in an original way, and iteratively decoded one after another, could do better than convolutional codes, which are based on very large states. This new coding scheme was named Turbo codes (Berrou et al . 1993). The era of iterative coding schemes was born, which resulted in a re-discovery of LDPC codes by MacKay and Neal (1997) that originally had already been published by Gallager in 1962 (Gallager 1962). Due to their excellent communications performance, consumer-driven cellular and broadcast communication standards such as UMTS, LTE, DVB and WiMAX, to name a few, adopted these new codes. A further breakthrough happened in 2009 when Erdal Arikan published Polar codes and proved that these codes could achieve channel capacity for a Binary Symmetric Memoryless Channel Binary Symmetric Memoryless Channel (BSMC) (Arikan 2009). Due to their excellent communications performance, Polar codes have attracted significant attention and became, for the first time, part of the 5G standard. For high throughput and low latency, these advanced decoding schemes, however, imply large challenges for efficient hardware implementation in consumer devices, where silicon area and power are the most critical cost factors. The computational workload of channel decoding for these advanced coding schemes with throughput in the Gbit/s range is more than 1,000 GOP/s (equivalent DSP operations). It is even more challenging with regard to the available power budget that is limited to some Watts for baseband processing due to thermal power density constraints. The high design costs of a baseband chip in advanced semiconductor technology demands for a large volume. This means that the corresponding SoC has to be used in various applications and the Forward Error Correction (FEC) Intellectual Property (IP) must be flexible to support various coding schemes, code rates, data rates, latency and BER/FER requirements. As mentioned earlier, adding flexibility to any architecture has a negative impact on throughput, energy efficiency, and area. Researchers are continuously looking for techniques to reduce the hardware implementation complexity and optimize energy efficiency for these advanced coding schemes while minimizing the degradation in communications performance (Kienle et al . 2011). Because of the aforementioned reasons, state-of-the-art channel decoders are typically implemented as dedicated accelerator cores. This can be seen in the wireless accelerator group depicted in Figure 2.1, that contains different types of channel en-/decoding accelerators to support various standards: an Application-Specific Instruction Set Processor (ASIP) that offers large flexibility for 2G/3G convolutional and Turbo code support (Vogt and Wehn 2008) and dedicated highly optimized LTE Turbo and DVB-S2 LDPC en-/decoders (Muller et al . 2009; Weithoffer et al . 2018).

Читать дальше