Philippe Darche - Microprocessor 4

Здесь есть возможность читать онлайн «Philippe Darche - Microprocessor 4» — ознакомительный отрывок электронной книги совершенно бесплатно, а после прочтения отрывка купить полную версию. В некоторых случаях можно слушать аудио, скачать через торрент в формате fb2 и присутствует краткое содержание. Жанр: unrecognised, на английском языке. Описание произведения, (предисловие) а так же отзывы посетителей доступны на портале библиотеки ЛибКат.

- Название:Microprocessor 4

- Автор:

- Жанр:

- Год:неизвестен

- ISBN:нет данных

- Рейтинг книги:4 / 5. Голосов: 1

-

Избранное:Добавить в избранное

- Отзывы:

-

Ваша оценка:

- 80

- 1

- 2

- 3

- 4

- 5

Microprocessor 4: краткое содержание, описание и аннотация

Предлагаем к чтению аннотацию, описание, краткое содержание или предисловие (зависит от того, что написал сам автор книги «Microprocessor 4»). Если вы не нашли необходимую информацию о книге — напишите в комментариях, мы постараемся отыскать её.

Microprocessor 4 — читать онлайн ознакомительный отрывок

Ниже представлен текст книги, разбитый по страницам. Система сохранения места последней прочитанной страницы, позволяет с удобством читать онлайн бесплатно книгу «Microprocessor 4», без необходимости каждый раз заново искать на чём Вы остановились. Поставьте закладку, и сможете в любой момент перейти на страницу, на которой закончили чтение.

Интервал:

Закладка:

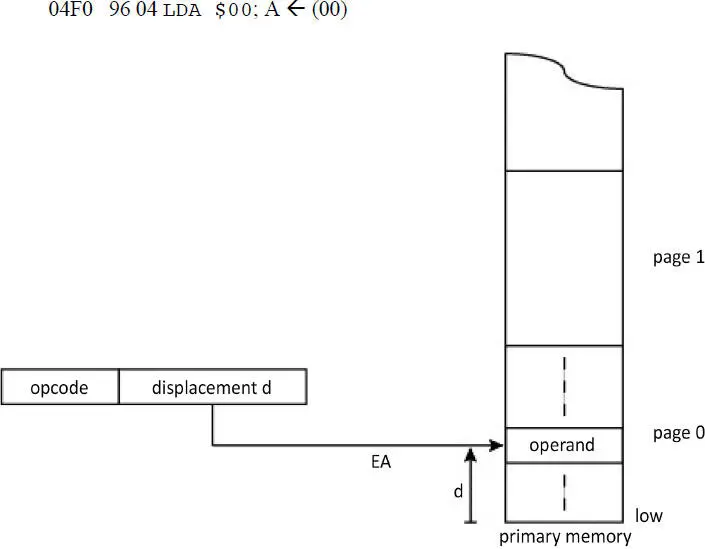

Figure 1.11. Instruction with an address at page 0

The concept of page zero addressing has been improved with direct page addressing. The direct page is now movable in a larger memory page. The start of the page is addressed by a specialized register ( cf . § V3-3.1.1). We cite MC6809 (a page of 256 bytes in a space of 64 KiB, addressing capacity of the MPU itself, direct page (DP) register), the 65CE02 from Commodore Semiconductor Group or CSG (the same as before except that its addressing capacity is higher, base page register B) and the 65816 from the firm Western Digital Corporation (WDC) with an address over 16 bits in the direct page register D.

A direct addressing is limited in its extent for a given instruction format; there are bits reserved for coding the instruction, which should be subtracted from the bits reserved for the addressing. This limitation can be lifted if the instruction format is not limited (i.e. variable format). With extended addressing, the address belongs to the microprocessor's address space without restriction. The format is that of the address bus. It should be noted that the absolute address can be implemented with a basic address + displacement with a basic register with zero content base.

1.2.3.2. Relative addressing

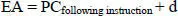

Relative addressing, implied in PC (Program Counter-relative addressing), makes it possible to access a memory location relating to the current position of the program counter that, we recall, contains the address of the next instruction to be executed (Figure 1.12) after the decoding stage. This mode is in fact an indexed mode using the PC ( cf . § 1.2.3.4 on indexing). With the following formula, we see that the effective address of the data or instruction relates to the PC by a value of d:

[1.2]

This is the favored mode for jump instructions, whether conditional or not (PC-relative branch). The relative displacement d is expressed in a signed integer representation, which is always the complement to 2 n(two's complement, cf . § II.2.5 from Darche (2000)). Depending on the size of the displacement, the extent of the jump will be limited to (-2 n-1, 2 n-1-1), with n being the format of the address field. Depending on the value of n of the relative address, we will call it a short or long jump. When the processor uses segmentation (this will be covered in a future book by the author on memories), jumps can be made within a single segment (intrasegment jump) or between two segments (extra-segment jump).

Figure 1.12. Execution of an instruction in relative addressing

The example below (x86) is a negative jump. The hexadecimal value F9 represents -7 in base 10. This means that the processor will connect 5 bytes higher than the instruction address, the difference of two bytes arising from the fact that the PC has changed while the instruction was executed (incrementation of the size of this instruction, here, two bytes):

73 F9 jnc loop; PC ← PC + F916

Two particular cases should be cited: jmp 00, which jumps to the following instruction since the program counter has been incremented during the decoding phase of the execution cycle ( cf . § V1-3.2 and V1-3.3.2) to direct the following instruction and jump –n, where n is the instruction format (in words) underway, which implements an infinite loop. This mode is linked to PC (PC with displacement or Program Counter with Displacement for MC68000). It can be seen as an indexed mode, the indexation register being the PC ( cf . § 1.2.3.4).

This mode is useful for generating the independent code of implantation in memory (position-independent code). We also speak of a translatable code (relocatable code), a topic discussed in § 3.1.4. It is also at the root of implantation of classic control structures of high-level languages (if__then_else, iterative structures (i.e. loops) such as while__do, repeat_until_, for__do, etc.) in assembly language.

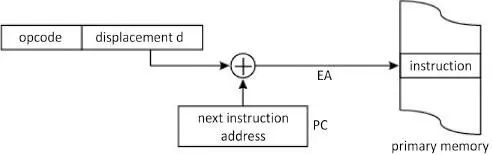

This mode can even be used to address an operand (Figure 1.13). We cite x86 64-bit architectures with addressing called RIP (Instruction Pointer Register)- relative, ARMv8 with literal mode and MPU MC6809 with the program counterrelative mode.

Figure 1.13. Seeking an operand in relative addressing

This mode can be seen as an indirect mode auto-incrementation using the PC (Program Counter) as an indirection register ( cf . § 1.2.3.3).

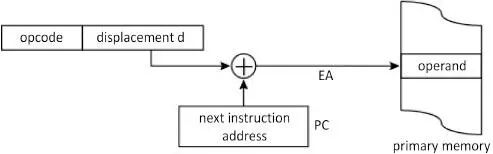

1.2.3.3. Indirect addressing

It is useful to dissociate addressing of the operand from that of the instruction code. The address may thus vary without changing the reference indicated in the instruction. This mode is used to implement the mechanism of the High-Level (programming) Language (HLL) pointer. In assembly language, the square brackets “[“ and “]” are generally used to employ this mode. Some constructors use parentheses or the character @. A memory location or register contains the address of the operand. In indirect mode or register deferred mode (register indirect or register deferred addressing 7) illustrated in Figure 1.14, the effective address EA is given by the following formula:

[1.3]

Figure 1.14. Instruction with indirect register addressing

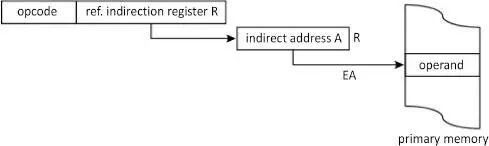

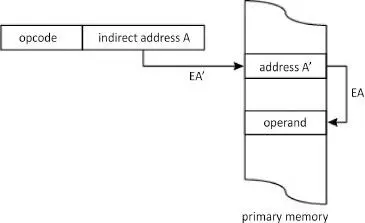

In memory indirect addressing illustrated in Figure 1.15, the final effective address EA is given by formula [1.5]. Here, it is a double indirection:

[1.4]

[1.5]

Figure 1.15. Instruction with indirect memory addressing

This mode of addressing generally has a greater extent than direct addressing since the addressing format m is the same as that of the data format n. It was therefore useful for the first computers, which had a restricted addressing capacity (in the case of mini-PDP-8 computers from the DEC firm of the NOVA series from Data General, for example). Another advantage is the decrease in the instruction format, thus increasing the instruction throughput. For MC6809, the constructor speaks of “extended indirect addressing”. The compiler will doubtlessly use this mode to implement the high-level language pointer mode such as C or Pascal by putting the value of the pointer (i.e. an address) in the indirection register.

Читать дальшеИнтервал:

Закладка:

Похожие книги на «Microprocessor 4»

Представляем Вашему вниманию похожие книги на «Microprocessor 4» списком для выбора. Мы отобрали схожую по названию и смыслу литературу в надежде предоставить читателям больше вариантов отыскать новые, интересные, ещё непрочитанные произведения.

Обсуждение, отзывы о книге «Microprocessor 4» и просто собственные мнения читателей. Оставьте ваши комментарии, напишите, что Вы думаете о произведении, его смысле или главных героях. Укажите что конкретно понравилось, а что нет, и почему Вы так считаете.