Philippe Darche - Microprocessor 4

Здесь есть возможность читать онлайн «Philippe Darche - Microprocessor 4» — ознакомительный отрывок электронной книги совершенно бесплатно, а после прочтения отрывка купить полную версию. В некоторых случаях можно слушать аудио, скачать через торрент в формате fb2 и присутствует краткое содержание. Жанр: unrecognised, на английском языке. Описание произведения, (предисловие) а так же отзывы посетителей доступны на портале библиотеки ЛибКат.

- Название:Microprocessor 4

- Автор:

- Жанр:

- Год:неизвестен

- ISBN:нет данных

- Рейтинг книги:4 / 5. Голосов: 1

-

Избранное:Добавить в избранное

- Отзывы:

-

Ваша оценка:

- 80

- 1

- 2

- 3

- 4

- 5

Microprocessor 4: краткое содержание, описание и аннотация

Предлагаем к чтению аннотацию, описание, краткое содержание или предисловие (зависит от того, что написал сам автор книги «Microprocessor 4»). Если вы не нашли необходимую информацию о книге — напишите в комментариях, мы постараемся отыскать её.

Microprocessor 4 — читать онлайн ознакомительный отрывок

Ниже представлен текст книги, разбитый по страницам. Система сохранения места последней прочитанной страницы, позволяет с удобством читать онлайн бесплатно книгу «Microprocessor 4», без необходимости каждый раз заново искать на чём Вы остановились. Поставьте закладку, и сможете в любой момент перейти на страницу, на которой закончили чтение.

Интервал:

Закладка:

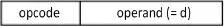

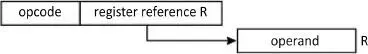

Figure 1.8. Instruction with an operand field

It is one of the fastest addressing modes since the value is included in the instruction and there is therefore no additional access to the main memory to fetch the operand accessed by another addressing. But this value is a constant. In addition, from the perspective of programming, the change of value means a modification in the program since the value field cannot be a destination. The extent of the values (in the sense of Chapter 2of Darche (2000)) is limited by the number of bits remaining after subtraction of those bits reserved for coding the operation itself (a similar limitation for the address for direct and relative addressing). In its extended or long version, the format is double that of a short format. The possibility of choosing makes it possible to decrease the number of clock cycles to fetch the operand. An alternative to this mode is register addressing, which contains a constant value, which is materially fixed. This is the current practice with RISC microprocessors (this will be covered in a future book by the author on microprocessors) such as Arm ®, whose register r0 contains the null value ( cf . § V3-3.1), which can serve for initialization and avoids time-consuming external access to the main memory.

1.2.2. Register addressing

The use of registers makes it possible not to slow the microprocessor down since the registers are integrated. An instruction that uses them in addressing mode will only require external access to fetch the instruction code. It is possible to address a register in two ways, explicitly and implicitly.

1.2.2.1. Explicit addressing

The operand field operand(s) R specifies the registers used for execution. It is sometimes called register (direct) addressing, the term “direct” indicating that the referencing in the register is found in the instruction coding, as for the direct memory address (Figure 1.9). These registers are accessible to the programmer. There is no effective address since the memory is not addressed, hence a fast execution of the instruction using it and a small instruction format. It is for this reason that RISC microprocessors prefer to use this mode. For other architectures, the number of registers accessible to the programmer is limited (order of size: about 20).

Figure 1.9. Execution of an instruction using register addressing from one register

The example below shows an addition in an Arm ®microprocessor, which uses three registers: r0, r1 and r2:

ADD r0,r1,r2; r0 ← r1 + r2

Note, a distinction can be made between Data Register Direct Addressing and Address Register Direct Addressing as for MC68000 ( cf . § V3-3.1.1).

1.2.2.2. Implicit register addressing

To simplify the programming, some instructions use one or more registers in an extended or implicit manner. In this addressing mode, also called implicit or implied addressing mode, no operand is specified after the instruction mnemonic ( cf . § 2.1). Execution of the instruction involves the reference to operand that is not joined to the operating code. One synonym is implication (Brooks 1962). The instruction format is reduced by it. One example is the dexinstruction from MCS6502, which decrements its index register X. The name of this appears in the mnemonic to facilitate programming. Sometimes when the accumulators are used, this mode is called “accumulator addressing”. The example below applied to MC6809. The accumulator B specified by the last letter of the mnemonic receives a value expressed in hexadecimal base.

LDB #$FA; B ← FA16

If the name of the registers does not appear in the mnemonic, then only a detailed reading of the technical documentation can specify the name of these registers. In the example below (MC6809), the instruction for multiplication mul (without operands) implicitly uses both implicit accumulator registers A and B and stores the concatenated result in these same registers, and the MSB (Most Significant Byte) is found in accumulator A, which in pseudo-code gives: A:B ← A × B.

Another example is the instruction from 8086 mul bl, which uses the implicit register A as source and destination operands in the case of multiplication in 8-bit format (ax ← bl × al for this example).

To generalize, an instruction lacking one or more operands found in a register (an accumulator for example) or in memory uses implicit addressing. We find this mode in machines with a single address called an accumulator or in the extreme case of zero-operand computers also called stack or pushdown-store machine ( cf . § V1-2.7.1). By broadening the definition to registers that are not accessible to the programmer, any instruction for its execution uses the PC (Program Counter), which is therefore implicit.

1.2.3. Memory addressing modes

It is possible to address the memory in a direct, relative, indirect, indexed or based manner. Combinations of these modes are possible. Other specific modes are then presented.

1.2.3.1. Direct addressing

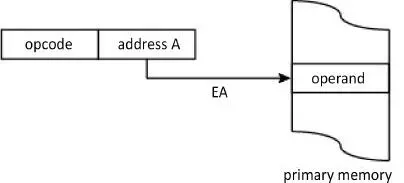

Direct or absolute addressing is without doubt the most natural. It can access a memory address location A defined (i.e. arranged immediately) after the instruction code in the operand field (Figure 1.10). It can therefore be considered a constant. The effective address EA is given by the following formula:

[1.1]

Figure 1.10. Instruction with direct addressing

It can be used by jump instruction to branch to a set location in the program. This mode is in fact an indirect mode with auto-incrementation using the PC (Program Counter) as an indirection register ( cf . § 1.2.3.3 for indirection).

This mode allows for variations depending on the format of the address provided, the benefit lies in reducing the instruction's memory size. Some manufacturers thus distinguish the short mode from the extended mode, known as long mode, depending on the format of the address A, provided. In the short mode (absolute short, page zero, also known direct at Motorola, a base page (IEEE 1985)) illustrated in Figure 1.11, the address is expressed in a smaller format than that of a microprocessor. The address field may also be smaller than 3 bits, one example being the 8021 microcontroller from Intel or, classically, 8 bits in 8-bit MPUs. Page zero can be seen as a bank of registers (RF for Register File, cf . § V3-3.1.11.1). The MIPS firm speaks of pseudo-direct addressing. Aside from a smaller format, the second benefit lies in decreasing the number of memory accesses to fetch the instruction code and the operand address. It is equivalent to a basic addressing + displacement, as in the IBM System/370 architecture, with a null base address. One example is the MC6802 microprocessor where the address is in byte format, while the format of the MPU address bus is double. This then limits the address space to the interval [00, FF] 16, hence the term “absolute short addressing” or “page zero” 6(if the size of the memory page is 256 bytes). In the example below, the A register receives the content of memory location 00.

Читать дальшеИнтервал:

Закладка:

Похожие книги на «Microprocessor 4»

Представляем Вашему вниманию похожие книги на «Microprocessor 4» списком для выбора. Мы отобрали схожую по названию и смыслу литературу в надежде предоставить читателям больше вариантов отыскать новые, интересные, ещё непрочитанные произведения.

Обсуждение, отзывы о книге «Microprocessor 4» и просто собственные мнения читателей. Оставьте ваши комментарии, напишите, что Вы думаете о произведении, его смысле или главных героях. Укажите что конкретно понравилось, а что нет, и почему Вы так считаете.