Philippe Darche - Microprocessor 4

Здесь есть возможность читать онлайн «Philippe Darche - Microprocessor 4» — ознакомительный отрывок электронной книги совершенно бесплатно, а после прочтения отрывка купить полную версию. В некоторых случаях можно слушать аудио, скачать через торрент в формате fb2 и присутствует краткое содержание. Жанр: unrecognised, на английском языке. Описание произведения, (предисловие) а так же отзывы посетителей доступны на портале библиотеки ЛибКат.

- Название:Microprocessor 4

- Автор:

- Жанр:

- Год:неизвестен

- ISBN:нет данных

- Рейтинг книги:4 / 5. Голосов: 1

-

Избранное:Добавить в избранное

- Отзывы:

-

Ваша оценка:

- 80

- 1

- 2

- 3

- 4

- 5

Microprocessor 4: краткое содержание, описание и аннотация

Предлагаем к чтению аннотацию, описание, краткое содержание или предисловие (зависит от того, что написал сам автор книги «Microprocessor 4»). Если вы не нашли необходимую информацию о книге — напишите в комментариях, мы постараемся отыскать её.

Microprocessor 4 — читать онлайн ознакомительный отрывок

Ниже представлен текст книги, разбитый по страницам. Система сохранения места последней прочитанной страницы, позволяет с удобством читать онлайн бесплатно книгу «Microprocessor 4», без необходимости каждый раз заново искать на чём Вы остановились. Поставьте закладку, и сможете в любой момент перейти на страницу, на которой закончили чтение.

Интервал:

Закладка:

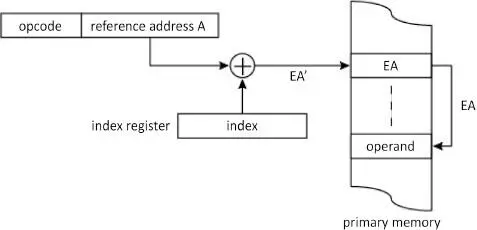

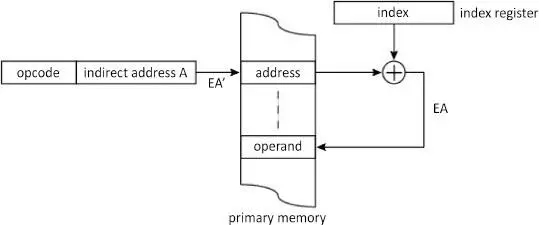

Figure 1.19 shows the mechanism. One example was MCS6502, which included two registers called “index registers X and Y” even though X has already served for indirection. Its designer calls this mode (indirect,X), which is justified by the relationship [1.8]. It was also suggested by MC6809. DEC used the term “index deferred addressing mode”.

Figure 1.19. Indirect indexed addressing or pre-indexing

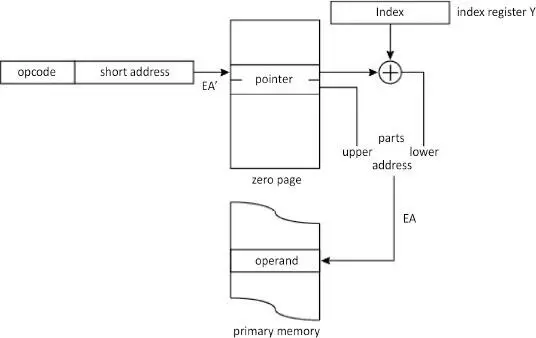

Post-indexed indirect addressing mode or indirect indexed addressing mode applies indexing after indirection, as illustrated in Figure 1.20. We will have:

[1.9]

[1.10]

Figure 1.20. Indirect indexed addressing or post-indexing

The peculiarity of MCS6502 is that it used zero-page addressing as the address field was limited to 8 bits and the indexing occurred only on the lower part of the address (Figure 1.21). Its designer calls this mode (indirect),Y, which is justified by the relationship [1.10].

Figure 1.21. Indirect indexed zero-page addressing of MCS6502

A representative, penultimate example is MC6809, which offers 18 variations in mode, combining indexed and indirect addressings with the possibility of automatic post-increment or pre-decrement. This post-increment or pre-decrement is useful for managing a stack's pointer. Table 1.2 summarizes the possible combinations. R represents one of the four registers that can be used for indexing, the classics X and Y and the stack pointers user U and material S. Note the addressings using the program counter at the end. The offset is expressed in complement to 2 nrepresentation.

Indexed and based addressings with or without offset (based indexed plus displacement addressing mode) can be combined, thus offering, for example, 17 possible variations in the case of microprocessor x86. One example of this use is addressing an array of records, of a vector or of a structure, the base pointing the start of the array and index, an element of the array and the displacement, a field of the element.

Table 1.2. Combined MC6809 addressing modes

| MC6809 assembly language notation | Description |

| ,R | Zero-offset indexed |

| [,R] | Zero-offset indexed indirect |

| ,R+ | Zero-offset indexed post-increment of 1 (auto-increment R) |

| ,R++ | Zero-offset indexed post-increment of 2 (auto-increment R) |

| [,R++] | Zero-offset indexed post-increment of 2 indirect (auto-increment R) |

| ,-R | Zero-offset indexed pre-decrement of 1 (auto-decrement R) |

| ,--R | Zero-offset indexed pre-decrement of 2 (auto-decrement R) |

| [,--R] | Zero-offset indexed pre-decrement of 2 indirect (auto-decrement R) |

| n,R | Constant signed offset indexed (5, 8 or 16 bits offset from R) |

| [n,R] | Constant signed offset indexed indirect (5, 8 or 16 bits offset from R) |

| A,R | Accumulator A signed offset from R indexed |

| [A,R] | Accumulator A signed offset from R indexed indirect |

| B,R | Accumulator B signed offset from R indexed |

| [B,R] | Accumulator B signed offset from R indexed indirect |

| D,R | Accumulator D signed offset from R indexed |

| [D,R] | Accumulator D signed offset from R indexed indirect |

| n,PCR | Constant signed offset from PC indexed (8 or 16 bits) |

| [n,PCR] | Constant signed offset from PC indexed indirect (8 or 16 bits offset) |

| [n] | Extended indirect |

1.2.4. Other addressing modes

Other modes have been introduced to provide a high-level functionality or to adapt to a specific domain such as digital signal processing ( cf . § V3-5.2), to a specific mechanism of a processor or to a component such as an I/O controller ( cf . Chapter 3of Darche (2003)) or a microcontroller ( cf . § V3-5.3). Moreover, other modes belong to high-level languages. To finish, some obsolete modes are presented.

1.2.4.1. Memory-to-memory addressing

The memory-to-memory transfer functionality is possible in a von Neumann- inspired MPU, but it should be seen as exceptional. This is the continuity of the tendency of CISC processors to implement high-level functionalities in the material. Intel calls this mode “string addressing” for its 8086. It involves addressing the characters of a string, that is, of an array of characters by indirection using both its pointer registers SI (Source Index) and DI (Destination Index). It makes it possible, among other things, to read or write a character and, whether the repeat prefix is conditional or not, to make a copy of it in the main memory. The search function in a string is also available.

1.2.4.2. (Implicit) stack addressing

Operands are found implicitly (i.e. they are not named) on the stack which is, we recall ( cf . § 4.1), access to LIFO (Last-In/First-Out, push-in/pop-out or push- down/pop-up memory) and implemented in primary memory in modern MPU. The two primitives (i.e. functions) to access it are stacking() and unstacking(), translated into instructions respectively by push()and pop(), for example, in x86 architecture. These instructions implement, internally, an indirect addressing mechanism with the Stack Pointer register (SP), which memorizes the address at the top of the stack. The stack is implemented in main memory, but it can be implemented in the processor. The stacked element is specified with the operand. There are also specific instructions to a register, such as pha/pla(push/pull accumulator onto/from stack) from MC6800, which makes it possible to stack/destack this MPU's accumulator. MCS6502 uses php/plp(push/pull processor status on/from stack) this time for the MPU's context. By extension, stack computers do not explicitly name the operands (zero-operand, one-operand or two-operand addressing). For reading on this subject, see Koopman (1989).

The NS3200 (Hunter 1987) from National Semiconductor (NS) has broadened access to the stack by offering a mode called top-of-stack, literally “stack top”, which makes it possible to access the data of the so-called summit, since modification of the pointer is not systematic (i.e. dependent on the operation). To finish with this topic, MPUs such as the families Arm ®, PowerPC or MC68000 make it possible to use General-Purpose Registers (GPR) as stack pointers. The addressing mode is of indirect type with auto-increment/decrement.

1.2.4.3. Bit addressing

Интервал:

Закладка:

Похожие книги на «Microprocessor 4»

Представляем Вашему вниманию похожие книги на «Microprocessor 4» списком для выбора. Мы отобрали схожую по названию и смыслу литературу в надежде предоставить читателям больше вариантов отыскать новые, интересные, ещё непрочитанные произведения.

Обсуждение, отзывы о книге «Microprocessor 4» и просто собственные мнения читателей. Оставьте ваши комментарии, напишите, что Вы думаете о произведении, его смысле или главных героях. Укажите что конкретно понравилось, а что нет, и почему Вы так считаете.