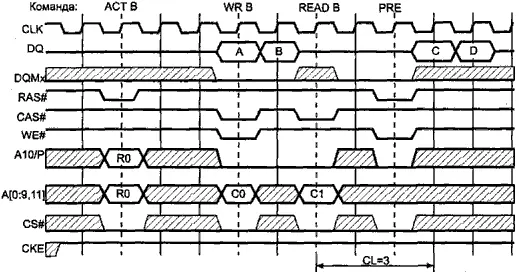

Рис. 7.6. Временные диаграммы пакетных циклов SDRAM: А и В — данные для записи по адресу R0/C0 и R0/C0+1, С и D — данные, считанные по адресу R0/C1 и R0/C1 +1

Регенерация (цикл CBR с внутренним счетчиком адреса регенерируемой строки) выполняется по команде REF, которую можно вводить только при состоянии покоя ( idle ) всех банков.

Микросхемы SDRAM оптимизированы для пакетной передачи. У них при инициализации программируется длина пакета (burst length=1, 2, 4, 8 элементов), порядок адресов в пакете (wrap mode: interleave/linear — чередующийся/линейный) и операционный режим. Пакетный режим может включаться как для всех операций (normal), так и только для чтения (Multiple Burst with Single Write). Этот выбор позволяет оптимизировать память для работы либо с WB, либо с WT-кэшем.

Обратим внимание, что внутренний счетчик адреса работает по модулю, равному запрограммированной длине пакетного цикла (например, при burst length=4 он не позволяет перейти границу обычного четырехэлементного пакетного цикла).

Пакетные циклы могут прерываться (принудительно завершаться) последующими командами. При этом оставшиеся адреса отбрасываются, и прерывающий пакет будет иметь полную длину (если его самого не прервут).

В команде Writeимеется возможность блокирования записи данных любого элемента пакета — для этого достаточно в его такте установить высокий уровень сигнала DQM. Этот же сигнал используется и для перевода в высокоимпедансное состояния буферов данных при операции чтения.

Микросхемы SDRAM имеют средства энергосбережения , для управления ими используется вход разрешения синхронизации CKE.

В режиме саморегенерации (Self Refresh) микросхемы периодически выполняют циклы регенерации по внутреннему таймеру и не реагируют на внешние сигналы, поэтому внешняя синхронизация может быть остановлена.

Режимы пониженного потребления (Power Down Mode) устанавливаются при переводе CKEв низкий уровень командой NOPили INHBT. В этих режимах микросхема не воспринимает команд. Поскольку в данных режимах регенерация не выполняется, длительность пребывания в них ограничена периодом регенерации.

Если во время выполнения команды чтения или записи установить CKE=L, то микросхема перейдет в режим Clock Suspend Mode , в котором «замораживается» внутренняя синхронизация (нет продвижения данных) и не воспринимаются новые команды.

Для памяти SDRAM ключевыми параметрами являются:

♦ допустимая тактовая частота;

♦ CL (Cas Latency) — число скрытых тактов (2 или 3);

♦ T RCD— задержка RAS-CAS, выраженная в тактах (2 или 3);

♦ T RP— время предварительного заряда RAS;

♦ T RC— минимальное время цикла обращений к строкам одного банка;

♦ T AC— время задержки появления данных на выходе относительно фронта синхросигнала.

По тактовой частоте для SDRAM, применяемой в качестве ОЗУ PC-совместимых компьютеров, имеется три градации: PC66 (поначалу ее так не называли, поскольку другой и не было), PC100 и PC133 для максимальных частот 66,6, 100 и 133 МГц соответственно. Их ключевые параметры приведены в табл. 7.4. В обозначении быстродействия микросхем SDRAM обычно фигурирует T AC; период частоты синхронизации, естественно, не может быть меньше этой задержки. Микросхемы со спецификацией -10 могут устойчиво работать в модулях лишь на частоте 66 МГц. Микросхемы -8 могут работать на частоте 100 МГц, но, в зависимости от модификации, с разной латентностью. Так, например, для памяти Micron микросхемы с маркировкой -8А…-8С могут работать на частоте 100 МГц с CL = 3, a -8D или -8Е — с CL = 2.

Таблица 7.4. Ключевые параметры временной диаграммы SDRAM

| Спецификация |

CL |

T RCD |

T RP |

T RC |

Примечание |

| PC66 |

3 |

2 |

3 |

8 |

Медленный вариант |

| 2 |

2 |

2 |

7 |

Самый быстрый вариант |

| PC100 |

3 |

3 |

3 |

8 |

Медленный вариант |

| 3 |

2 |

2 |

7 |

Средний вариант |

| 2 |

2 |

2 |

7 |

Самый быстрый вариант |

| PC133 |

3 |

3 |

3 |

9 |

Медленный вариант |

| 3 |

2 |

2 |

8 |

Средний вариант |

| 2 |

3 |

2 |

8 |

Средний вариант |

| 2 |

2 |

2 |

8 |

Самый быстрый вариант |

Естественно, память может работать и на частотах ниже максимальной. Для микросхем SDRAM, применяемых, например, в графических адаптерах, существуют и иные спецификации быстродействия.

Синхронный интерфейс позволяет довольно эффективно использовать шину и обеспечить на частоте 100 МГц пиковую производительность 100 Мбит/с на 1 вывод шины данных. SDRAM используют в составе модулей DIMM с 8-байтной разрядностью, что дает производительность 800 Мбайт/с. При частоте шины 133 МГц пиковая производительность уже достигла 1064 Мбайт/с. Однако эта теоретическая производительность не учитывает накладные расходы на регенерацию и подразумевает, что требуемые страницы уже открыты. Из-за указанных выше ограничений на реальном произвольном потоке запросов производительность, конечно же, будет ниже. Потенциальные возможности почти одновременного обслуживания множества запросов, предоставляемые микросхемами SDRAM, будут реализованы лишь при достаточно «умном» контроллере памяти. От его предусмотрительности эффективность памяти зависит, пожалуй, больше, чем у простых модулей FPM и EDO DRAM.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)