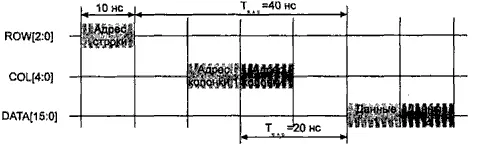

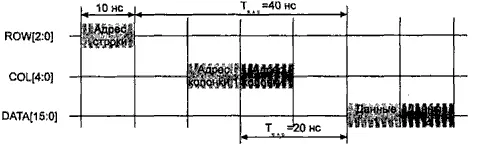

Рис. 7.9. Транзакции чтения RDRAM

Транзакции записи (рис. 7.10) являются однонаправленными и для них проблем синхронизации не возникает. В отличие от стандартных микросхем DRAM и SDRAM, где данные для записи передаются одновременно с адресом колонки, в RDRAM данные задерживают относительно пакета COLCна T CWD(несколько тактов). Эта задержка соответствует задержке между пакетами COLCи данными при чтении (на стороне контроллера). Задержка записи позволяет сократить вынужденные простои шины данных при переключении с записи на чтение (в SDRAM они равны CAS Latency и длятся 2–3 такта по 10 нс). Контроллер может посылать данные для записи уже в такте, следующим за последними данными предыдущей транзакции чтения. Однако если за записью следует чтение, то на шине данных будет вынужденная пауза в 1–5 тактов в зависимости от длины канала. За это время последние данные записи дойдут от контроллера до самой дальней микросхемы памяти.

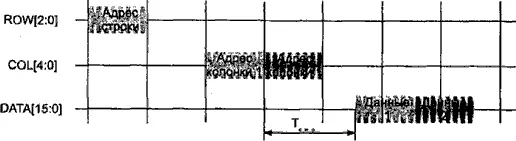

Рис. 7.10. Транзакции записи RDRAM

В микросхемах RDRAM применяется механизм отложенной , или буферированной , записи. Данные для записи (принятый пакет D) сначала помещаются в буфер, из которого несколько позже они выгружаются в усилители считывания-записи (sens amp) по явной команде выгрузки (retire) или автоматически. Буфер записи хранит сами данные, а также номер банка и адрес столбца (но не строки). Буферизация записи позволяет контроллеру посылать команду записи на T RTRраньше, чем этого требует параметр T RCD, что повышает коэффициент использования шины.

Конвейерное выполнение операций RDRAM обеспечивается многобанковой организацией с отдельными усилителями считывания. Пакеты команд по линиям ROW и COL могут идти сплошным потоком, при этом на шине может присутствовать до четырех транзакций. При произвольных обращениях увеличению производительности способствует большое количество банков, практически недостижимое в памяти SDRAM.

Регенерация осуществляется по команде, адресуемой к определенному банку одной или всех микросхем; за период регенерации эта команда должна выдаваться для всех банков.

Память RDRAM отличается высоким энергопотреблением. Средства управления энергопотреблением отключают питание неиспользуемых узлов, однако за 100-кратное снижение мощности в самом экономичном режиме приходится расплачиваться 250-кратным увеличением времени доступа. Микросхемы RDRAM требуют периодической (раз в 100 мс) подстройки выходного тока и термокалибровки; для этих целей имеются специальные команды. Во время подстройки тока микросхемы способны сообщать о своем перегреве.

Вспомогательная шина с сигналами SCK, CMDи SIOслужит для обмена данными с управляющими регистрами и вывода микросхем из состояний пониженного потребления ( PDN и NAP ). Информация по этой шине тоже передается пакетами.

Управляющие регистры хранят информацию об адресе микросхемы, управляют работой микросхемы в различных режимах, содержат счетчики регенерации для банков и строк, параметры настройки временных циклов. В них же можно прочитать информацию о конкретной микросхеме — организация, версия протокола и т. п. В составе управляющих есть и тестовые регистры.

Инициализация памяти включает определение наличия микросхем на шине, назначение им идентификаторов и программирование их параметров. После сброса микросхемы не имеют собственных адресов, а линии SIO0и SIO1у них соединены. В таком состоянии контроллер по шине CMDпосылает широковещательную команду на разъединение линий, после чего для него по линии SIOоказывается доступной только ближайшая микросхема канала. Ей назначается адрес ( SDEVID) и дается команда на соединение линий, в результате к контроллеру подключается вторая микросхема. Она будет пронумерована очередной командой, заставляющей все доступные ненумерованные микросхемы (то есть именно ее) принять указанный номер. Далее замыкаются ее линии SIO, и этот процесс продолжается до самой дальней микросхемы.

После завершения этого «переучета» включается нормальная синхронизация, и дается время для установления режима схем DLL. После двукратной активации и предварительного заряда каждого банка каждой микросхемы память готова к определению доменов синхронизации и назначению каждой микросхеме соответствующих параметров задержек. Также им должны быть присвоены идентификаторы в канале ( DEVID), которые могут и не совпадать со значениями SDEVID(идентификатором на последовательной шине).

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)