Динамическая память — DRAM (Dynamic RAM) — получила свое название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов, образованных элементами полупроводниковых микросхем. При отсутствии обращения к ячейке со временем за счет токов утечки конденсатор разряжается и информация теряется, поэтому такая память требует периодической подзарядки конденсаторов (обращения к каждой ячейке) — память может работать только в динамическом режиме. Этим она принципиально отличается от статической памяти, реализуемой на триггерных ячейках и хранящей информацию без обращений к ней сколь угодно долго (при включенном питании).

Запоминающие ячейки микросхем DRAM организованы в виде двумерной матрицы. Адреса строки и столбца передаются по мультиплексированной шине адреса MA(Multiplexed Address) и стробируются по спаду импульсов RAS#(Row Access Strobe) и CAS#(Column Access Strobe). Состав сигналов микросхем динамической памяти приведен в табл. 7.1.

Таблица 7.1. Сигналы микросхем динамической памяти

| Сигнал |

Назначение |

| RAS# |

Row Access Strobe — строб выборки адреса строки. По спаду сигнала начинается любой цикл обращения; низкий уровень сохраняется на все время цикла. Перед началом следующего цикла сигнал должен находиться в неактивном состоянии (высокий уровень) не менее, чем время предварительного заряда RAS (T RP— RAS precharge time) |

| CAS# |

Column Access Strobe — строб выборки адреса столбца. По спаду сигнала начинается цикл записи или чтения; минимальная длительность (T CAS) определяется спецификацией быстродействия памяти. Минимальная длительность неактивного состояния между циклами (высокий уровень) должна быть не менее, чем время предварительного заряда CAS (T CP— CAS precharge time) |

| MAi |

Multiplexed Address — мультиплексированные линии адреса. Во время спада сигнала RAS# на этих линиях присутствует адрес строки, во время спада CAS# — адрес столбца. Адрес должен устанавливаться до спада соответствующего строба и удерживаться после него еще некоторое время. Микросхемы с объемом 4 М ячеек могут быть с симметричной организацией — 11 бит адреса строк и 11 бит адреса колонок или асимметричными — 12×10 бит соответственно |

| WE# |

Write Enable — разрешение записи. Данные записываются в выбранную ячейку либо по спаду CAS# при низком уровне WE# (Early Write — ранняя запись, обычный вариант), либо по спаду WE# при низком уровне CAS# (Delayed Write — задержанная запись). Переход WE# в низкий уровень и обратно при высоком уровне CAS# записи не вызывает, а только переводит выходной буфер EDO DRAM в высокоимпедансное состояние |

| ОЕ# |

Output Enable — разрешение открытия выходного буфера при операции чтения. Высокий уровень сигнала в любой момент переводит выходной буфер в высокоимпедансное состояние |

| DB-In |

Data Bit Input — входные данные (только для микросхем с однобитной организацией) |

| DB-Out |

Data Bit Output — выходные данные (только для микросхем с однобитной организацией). Выходные буферы стандартных микросхем открыты только при сочетании низкого уровня сигналов RAS#, CAS#, OE# и высокого уровня WE#; при невыполнении любого из этих условий буферы переходят в высокоимпедансное состояние. У микросхем EDO выходные буферы открыты и после подъема CAS#. Логика управления предусматривает возможность непосредственного объединения выходов нескольких микросхем |

| DQx |

Data Bit — объединенные внутри микросхемы входные и выходные сигналы данных (объединение экономит количество выводов для микросхем с многобитной организацией) |

| N.C. |

No Connection — свободный вывод |

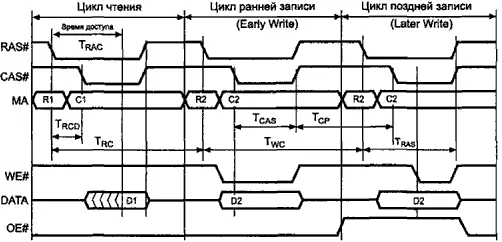

Выбранной микросхемой памяти является та, на которую во время активности (низкого уровня) сигнала RAS#приходит сигнал CAS#(тоже низким уровнем). Тип обращения определяется сигналами WE#и CAS#. Временная диаграмма «классических» циклов записи и чтения приведена на рис. 7.1. Как из нее видно, при чтении данные на выходе относительно начала цикла (сигнала RAS#) появятся не раньше, чем через интервал T RAC, который и является временем доступа .

Рис. 7.1. Временные диаграммы чтения и записи динамической памяти

Микросхемы DRAM имеют множество временных параметров, из которых выделим несколько важнейших, с которыми иногда приходится сталкиваться при настройке параметров циклов в CMOS Setup.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)