Hafiz M. H. Babu - Reversible and DNA Computing

Здесь есть возможность читать онлайн «Hafiz M. H. Babu - Reversible and DNA Computing» — ознакомительный отрывок электронной книги совершенно бесплатно, а после прочтения отрывка купить полную версию. В некоторых случаях можно слушать аудио, скачать через торрент в формате fb2 и присутствует краткое содержание. Жанр: unrecognised, на английском языке. Описание произведения, (предисловие) а так же отзывы посетителей доступны на портале библиотеки ЛибКат.

- Название:Reversible and DNA Computing

- Автор:

- Жанр:

- Год:неизвестен

- ISBN:нет данных

- Рейтинг книги:3 / 5. Голосов: 1

-

Избранное:Добавить в избранное

- Отзывы:

-

Ваша оценка:

Reversible and DNA Computing: краткое содержание, описание и аннотация

Предлагаем к чтению аннотацию, описание, краткое содержание или предисловие (зависит от того, что написал сам автор книги «Reversible and DNA Computing»). Если вы не нашли необходимую информацию о книге — напишите в комментариях, мы постараемся отыскать её.

‐bit parallel adder (carry‐out ignored).Figure 4.9 Illustration of the division circuit.

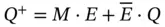

‐bit parallel adder (carry‐out ignored).Figure 4.9 Illustration of the division circuit. ) on the Fredkin gate.Figure 6.2 Mapping of variable

) on the Fredkin gate.Figure 6.2 Mapping of variable  (Equation J

(Equation J  ) on the Fredkin gate.Figure 6.3 Reversible design of

) on the Fredkin gate.Figure 6.3 Reversible design of  latch with minimal garbage outputs.Figure 6.4 Conventional cross‐coupled SR latch.Figure 6.5 Peres gate based SR latch without enable.Figure 6.6 Reversible SR latch based on modified truth table.Figure 6.7 Reversible gated SR latch based on modified truth table.Figure 6.8 Fredkin gate‐based D latch with one Feynman gate.Figure 6.9 Fredkin gate‐based D latch with two Feynman gates.Figure 6.10 Fredkin gate‐based negative enable reversible D latch with only ...Figure 6.11 Fredkin gate‐based negative enable reversible D latch with outpu...Figure 6.12 Peres gate‐based

latch with minimal garbage outputs.Figure 6.4 Conventional cross‐coupled SR latch.Figure 6.5 Peres gate based SR latch without enable.Figure 6.6 Reversible SR latch based on modified truth table.Figure 6.7 Reversible gated SR latch based on modified truth table.Figure 6.8 Fredkin gate‐based D latch with one Feynman gate.Figure 6.9 Fredkin gate‐based D latch with two Feynman gates.Figure 6.10 Fredkin gate‐based negative enable reversible D latch with only ...Figure 6.11 Fredkin gate‐based negative enable reversible D latch with outpu...Figure 6.12 Peres gate‐based  latch.Figure 6.13 Reversible T latch with outputs

latch.Figure 6.13 Reversible T latch with outputs  and

and  .Figure 6.14 Reversible JK latch with outputs

.Figure 6.14 Reversible JK latch with outputs  and

and  .Figure 6.15 Reversible master–slave D flip‐flop.Figure 6.16 Reversible master–slave T flip‐flop.Figure 6.17 Reversible master–slave JK flip‐flop.Figure 6.18 Reversible master–slave SR flip‐flop.Figure 6.19 Application of the Fredkin gate to avoid the fan‐out.Figure 6.20 Asynchronous reset of the

.Figure 6.15 Reversible master–slave D flip‐flop.Figure 6.16 Reversible master–slave T flip‐flop.Figure 6.17 Reversible master–slave JK flip‐flop.Figure 6.18 Reversible master–slave SR flip‐flop.Figure 6.19 Application of the Fredkin gate to avoid the fan‐out.Figure 6.20 Asynchronous reset of the  and

and  outputs of the Fredkin gate.Figure 6.21 Asynchronous set of the

outputs of the Fredkin gate.Figure 6.21 Asynchronous set of the  and

and  outputs of the Fredkin gate.Figure 6.22 Fredkin gate‐based asynchronous set/reset D latch.Figure 6.23 Reversible asynchronous set/reset master–slave D flip‐flop.

outputs of the Fredkin gate.Figure 6.22 Fredkin gate‐based asynchronous set/reset D latch.Figure 6.23 Reversible asynchronous set/reset master–slave D flip‐flop. flip‐flop.Figure 7.2 Reversible clocked T flip‐flop for synchronous counter.Figure 7.3 Reversible clocked T flip‐flop for asynchronous counter.Figure 7.4 Block diagram of

flip‐flop.Figure 7.2 Reversible clocked T flip‐flop for synchronous counter.Figure 7.3 Reversible clocked T flip‐flop for asynchronous counter.Figure 7.4 Block diagram of  MPG gate.Figure 7.5 Quantum representation of 3

MPG gate.Figure 7.5 Quantum representation of 3  3 MPG gate.Figure 7.6 Reversible master–slave T flip‐flop.Figure 7.7 4‐bit reversible asynchronous counter.Figure 7.8 4‐bit reversible synchronous counter.Figure 7.9 Quantum implementation of a reversible 2– to –4 decoder.Figure 7.10 Measurement of the quantum delay for the reversible 2– to –4 decod...Figure 7.11 Reversible 2– to –4 decoder.Figure 7.12 Reversible 4–to–2 encoder.

3 MPG gate.Figure 7.6 Reversible master–slave T flip‐flop.Figure 7.7 4‐bit reversible asynchronous counter.Figure 7.8 4‐bit reversible synchronous counter.Figure 7.9 Quantum implementation of a reversible 2– to –4 decoder.Figure 7.10 Measurement of the quantum delay for the reversible 2– to –4 decod...Figure 7.11 Reversible 2– to –4 decoder.Figure 7.12 Reversible 4–to–2 encoder. 3 reversible NH gate.Figure 10.2 Quantum realization of 3

3 reversible NH gate.Figure 10.2 Quantum realization of 3  3 reversible NH gate.Figure 10.3 Block diagram of 4

3 reversible NH gate.Figure 10.3 Block diagram of 4  4 reversible BSP gate.Figure 10.4 4‐to‐1 reversible MUX.Figure 10.5 Reversible D latch.Figure 10.6 Reversible Write‐Enabled Master–Slave flip‐flop.Figure 10.7 Block diagram of a reversible RAM.Figure 10.8 A reversible logic element of Plessey FPGA.Figure 10.9

4 reversible BSP gate.Figure 10.4 4‐to‐1 reversible MUX.Figure 10.5 Reversible D latch.Figure 10.6 Reversible Write‐Enabled Master–Slave flip‐flop.Figure 10.7 Block diagram of a reversible RAM.Figure 10.8 A reversible logic element of Plessey FPGA.Figure 10.9  Reversible MUX gate.Figure 10.10 Different uses of a Feynman gate.Figure 10.11 One template of toffoli gate.Figure 10.12 Two templates of MUX gate.Figure 10.13 Ex‐OR plane realization for the function F based on the Algorit...Figure 10.14 Design of reversible PLAs for multi‐output function F .Figure 10.15 Delay calculation of AND plane: (a‐b) delay propagation path of...Figure 10.16 Delay calculation of Ex‐OR plane: (a‐b) delay propagation path ...

Reversible MUX gate.Figure 10.10 Different uses of a Feynman gate.Figure 10.11 One template of toffoli gate.Figure 10.12 Two templates of MUX gate.Figure 10.13 Ex‐OR plane realization for the function F based on the Algorit...Figure 10.14 Design of reversible PLAs for multi‐output function F .Figure 10.15 Delay calculation of AND plane: (a‐b) delay propagation path of...Figure 10.16 Delay calculation of Ex‐OR plane: (a‐b) delay propagation path ...