Если же прикладная программа обслуживает достаточно динамичный объект, то может возникнуть необходимость выборки из регистров результата данных в процессе исполнения измерительной последовательности. Именно тогда и следует воспользоваться флагами завершения преобразования в отдельных каналах CCF7…CCF0. Прикладная программа должна запустить измерительную последовательность на исполнение, а затем контролировать состояние флага первого преобразуемого канала. Когда флаг установится, соответствующий регистр результата может быть считан. При этом во время выборки из памяти первого результата, будет продолжаться аналого-цифровое преобразование следующего сигнала. И так до завершения всей измерительной последовательности.

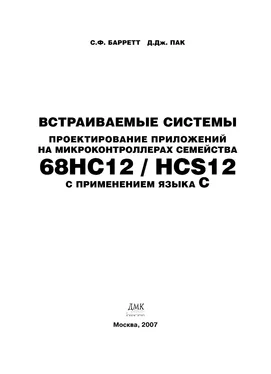

Программный опрос или поллинг (в англоязычной терминологии) — не единственный способ взаимодействия прикладной программы с модулем аналого-цифрового преобразования. Модуль ATD способен генерировать запросы на прерывание по завершению исполнения измерительной последовательности. Прерывания разрешаются посредством установки бита ASCIE регистра ATDCTL2 в 1. При этом запрос на прерывание генерируется, если устанавливается бит ASCIF в том же регистре. Этот же бит следует сбросить в подпрограмме прерывания, чтобы по завершению следующей измерительной последовательности был сгенерирован новый запрос. Обратите внимание на некоторую особенность битов состояния модуля ATD. Существует два бита завершения исполнения измерительной последовательности: бит ASCIF в регистре управления ATDCTL2 и бит SCF в регистре состояния ATDSTAT. При этом первый бит используется в прерываниях, а второй при программном опросе.

4.23. Особенности модуля ATD в составе МК семейства HCS12

Модуль ATD в составе МК семейства HCS12 по своей архитектуре и исполняемым функциям крайне близок к рассмотренному модулю аналого-цифрового преобразования микроконтроллеров семейства 68HC12. Однако он имеет ряд отличий, которые позволили улучшить его функциональные характеристики:

• Программируемая разрядность аналого-цифрового преобразования: 8 или 10 бит;

• Несколько способов представления результата преобразования: в формате со знаком и без знака, со сдвигом кода 10-разрядного кода в старшие или младшие разряды 16-разрядного регистра результата;

• Возможность запуска измерительной последовательности от внешнего сигнала;

• Программируемое от 1 до 8 число преобразований в одной измерительной последовательности;

• В некоторых моделях МК число аналоговых входов увеличено до 16.

Далее мы кратко остановимся на каждом из этих дополнительных свойств модуля ATD в составе МК HCS12.

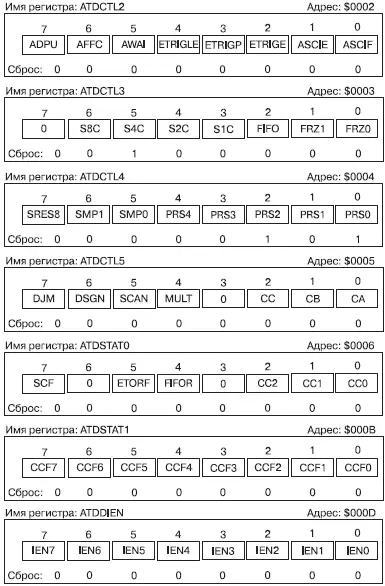

4.23.1. Выбор разрядности АЦП

Бит SRES8 в регистре управления ATDCTL4 (рис. 4.93) определяет число разрядов кода аналого-цифрового преобразования, которое выполняет встроенный АЦП модуля ATD. Использование 10-разрядного кода в представлении результата позволяет повысить разрешающую способность АЦП с 19,53 мВ до 4,88 мВ.

Рис. 4.93.Формат регистров модуля ATD в составе HCS12

4.23.2. Представление результата измерения

Результат аналого-цифрового преобразования модуля ATD может быть представлен в формате без знака или со знаком. Бит DSGN регистра ATDCTL5 (рис. 4.93) осуществляет выбор между представлением без знака (при DSGN = 0) или со знаком (при DSGN = 1). Код результата может размещаться со сдвигом влево, т.е. в старшие разряды 16-разрядного регистра результата (бит DJM = 0), или со сдвигом вправо, т.е. в младшие разряды регистра результата (бит DJM = 1).

4.23.3. Запуск измерительной последовательности от внешнего сигнала

Аппаратные средства модуля аналого-цифрового преобразования в составе МК HCS12 позволяют производить запуск измерительной последовательности по изменению внешнего сигнала, который подключается на вход AN7/ETRIG/PAD7 модуля. Такой режим чрезвычайно полезен для синхронизации проводимых измерений с режимами работы объекта управления. Режим внешнего запуска разрешается установкой бита ETRIGE регистра ATDCTL2 в 1. При ETRIGE = 0 реализуется обычный программный режим запуска.

Параметры внешнего сигнала запуска настраиваются посредством задания кодовой комбинации двух битов управления в регистре ATDCTL2. Бит ETRIGLE назначает запуск по уровню или по перепаду внешнего сигнала, бит ETRIGP определяет активный уровень сигнала запуска (логический 0 или 1). Формат обновленного регистра управления ATDCTL2 с перечисленными битами представлен на рис. 4.93. При ETRIGLE:ETRIGP = 00 реализуется запуск измерительной последовательности по спадающему фронту внешнего сигнала, при ETRIGLE:ETRIGP = 01 — по нарастающему фронту, при ETRIGLE:ETRIGP = 10 запуск осуществляется при низком логическом уровне внешнего сигнала, при ETRIGLE:ETRIGP = 11 — при высоком уровне сигнала.

Читать дальше