Ответ:

f S ≥ 2 f h = 2×20 = 40 кГц

5. Сколько бит данных в секунду генерирует 8-разрядный АЦП при частоте выборке сигнала 40 кГц?

Ответ:

f S× n = 40000 × 8 = 320000 бит/с

6. Предположим, что частотный диапазон музыкального сигнала составляет от 20 Гц до 20 кГц. Этот сигнал должен быть записан на компакт диск с использованием 16-разрядного АЦП, частоту дискретизации предполагается установить 44 кГц. Правильно ли выбрана частота дискретизации? Чему равна скорость потока данных при воспроизведении диска?

Ответ:

В соответствии с критерием Найквиста частота дискретизации выбрана верно. Она должна составлять не менее 220 кГц = 40 кГц. Выбранное значение 44 кГц превышает минимально необходимое значение частоты дискретизации. Скорость потока данных составляет:

f S× n × (число каналов) = 44000 × 16 × 2 = 1,41 Мб/с

4.21. Принцип действия АЦП

Известно несколько различных способов преобразования аналогового сигнала в цифровой код. Для большинства способов сигнал, подлежащий оцифровке, должен оставаться постоянным в течение всего времени аналого-цифрового преобразования. Поэтому большинство АЦП в качестве входной цепи используют так называемое устройство выборки и хранения (УВХ). УВХ — это электронная цепь с накопительным конденсатором, которой до начала преобразования заряжается до уровня измеряемого напряжения, затем напряжение на конденсаторе остается неизменным в течение времени преобразования. По способу преобразования различают следующие типы АЦП:

• последовательного приближения;

• двойного интегрирования;

• прямого счета;

• параллельные АЦП.

Мы рассмотрим только способ последовательного приближения, поскольку именно этот способ используется в модуле аналого-цифрового преобразователя МК семейства 68HC12/HCS12. Если у читателя возникнет желание познакомиться с другими способами преобразования, то он может обратиться к книге авторов Pack и Barret [2002].

4.21.1. АЦП последовательного приближения

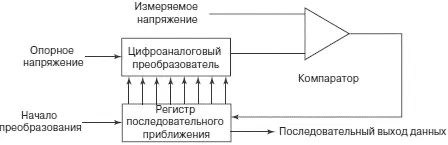

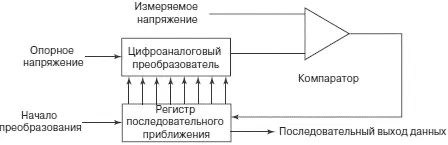

а) Функциональная схема

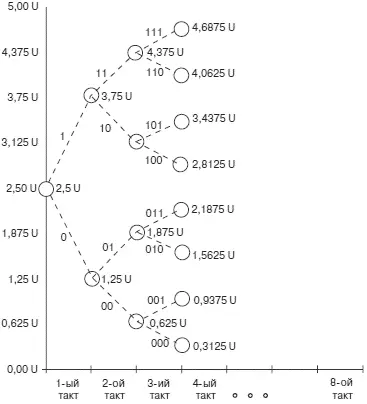

б) Диаграмма, поясняющая принцип действия АЦП последовательного приближения

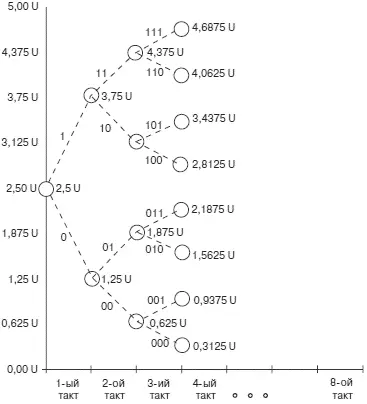

Рис. 4.82.Аналого-цифровой преобразователь последовательного приближения

Структурная схема АЦП последовательного приближения представлена на рис. 4.82. Алгоритм функционирования АЦП последовательного приближения рассмотрим на примере. Предположим, что вывод низкого уровня опорного напряжения V RL нашего АЦП подключен к потенциалу 0 В, а вывод высокого уровня опорного напряжения V HL — к потенциалу 5,0 В. АЦП формирует на выходе 8-разрядный двоичный код. Число различных кодов, которыми может быть представлен результат оцифровки, составляет 2 8= 256. Разрешающая способность нашего АЦП составляет:

(5,0 – 0,0)/256 = 19,53 мВ

Процесс аналого-цифрового преобразования по способу последовательного приближения многотактный. Число тактов, необходимое для выполнения одного преобразования, равно числу двоичных разрядов в представлении результата. Таким образом, в нашем примере на выходе АЦП будет сформирован восьмиразрядный двоичный код результата после завершения восьмого такта преобразования. Процесс преобразования запускается по сигналу Start.

Диаграмма рис. 4.82 отражает процесс формирования цифрового кода в АЦП последовательного приближения. На каждом такте формируется один двоичный разряд результата: на первом такте — старший разряд D7, на втором такте — разряд D6 и т.д., заканчивая младшим разрядом D0 на восьмом такте.

На первом такте в регистре последовательного приближения устанавливается код K1=10000000b. Этот код поступает на вход цифро-аналогового преобразователя (ЦАП), опорное напряжение которого равно U REF = U RH–U RL =5,0 В.

На выходе ЦАП установится напряжение U DAC = U REF× K1/2 8=2,5 В. Аналоговый компаратор сравнивает измеряемое напряжение U INP с напряжением на выходе ЦАП U DAC . Если U INP > U DAC , то на выходе компаратора формируется логическая 1. Если U INP < U DAC , на выходе компаратора устанавливается логический 0. Сигнал с выхода компаратора поступает на вход регистра последовательного приближения. Его значение определяет код на выходе регистра последовательного приближения в следующем такте преобразования. Если на выходе компаратора 1, то во втором такте преобразования регистр сформирует код K2 = 11000000b, если 0, то K2 = 01000000b. Иными словами, значение формируемого в текущем такте преобразования двоичного разряда равно значению логического сигнала на выходе компаратора.

Читать дальше