Формат второго регистра управления SPxCR2 контроллера SPI также приведен на рис. 4.72. Этот регистр содержит всего три бита управления:

PUPS:

Бит выбора схемотехники входных буферов порта S. Если этот бит равен 1, то все линии порта S, которые находятся в режиме ввода, переходят в состояние входа с внутренним подтягивающим к напряжению питания резистором.

RDS:

Бит выбора схемотехники выходных буферов порта S. Если этот бит равен 1, то все линии порта S, которые находятся в режиме вывода, переходят в состояние выхода с пониженной нагрузочной способностью.

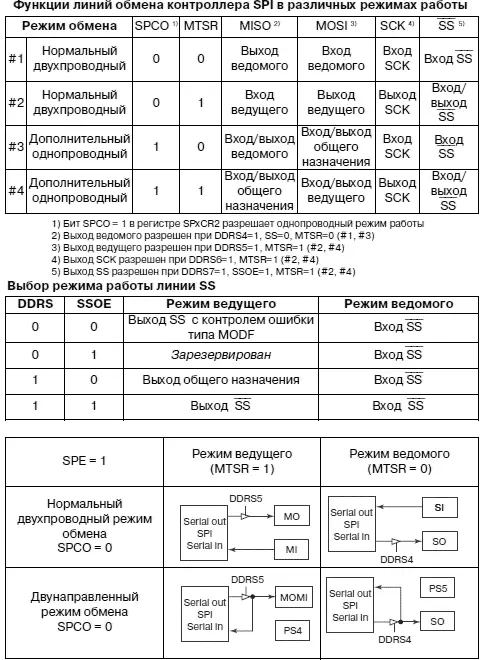

SPCO:

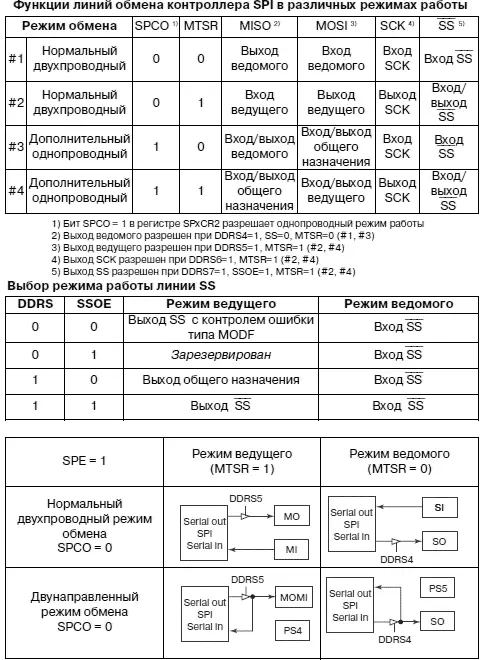

Совместно с битом MSTR этот бит определяет конфигурацию входов/выходов контроллера SPI на выводы корпуса МК в соответствие с таблицей рис. 4.73.

Познакомившись с назначением отдельных битов регистров управления SPxCR1 и SPxCR2, можно сказать, что эти регистры определяют конфигурацию аппаратных средств контроллера SPI. Разъясним дополнительно функции битов MSTR регистра SPxCR1 и SPCO регистра SPxCR2. Возможные комбинации кодов этих двух битов и соответствующие им внутренние соединения линии ввода и линии вывода контроллера SPI показаны на рис. 4.73. Например, если значения рассматриваемых битов равны SPCO:MSTR = 01, то вывод MISO будет выполнять функцию ввода данных, а вывод MOSI — функцию вывода данных контроллера SPI, работающего в режиме ведущего. Линия SCK при этом значении кодовой комбинации битов SPCO:MSTR будет использоваться для выдачи импульсов синхронизации, а линия  может быть дополнительно сконфигурирована на ввод или на вывод. Примечания 1–5 на рис 4.73 содержат дополнительную информацию по конфигурированию линий порта S для обслуживания контроллера SPI записи 0 или 1 в соответствующие разряды регистра направления передачи DDRS порта S. Мы рассмотрим эти рекомендации в примере программного обслуживания контроллера SPI (раздел 4.19.4).

может быть дополнительно сконфигурирована на ввод или на вывод. Примечания 1–5 на рис 4.73 содержат дополнительную информацию по конфигурированию линий порта S для обслуживания контроллера SPI записи 0 или 1 в соответствующие разряды регистра направления передачи DDRS порта S. Мы рассмотрим эти рекомендации в примере программного обслуживания контроллера SPI (раздел 4.19.4).

На рис. 4.73 показано, что выходы контроллера SPI могут работать как в нормальном двухпроводном режиме (обмен одновременно идет по линиям SI и SO), так и в однопроводном режиме (обмен идет по одной линии).

Рис. 4.73.Выбор режима работы контроллера SPI

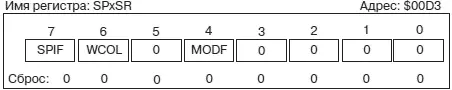

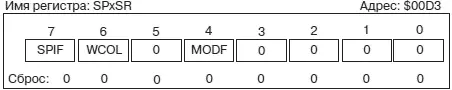

Формат регистра состояния SPxSR контроллера SCI представлен на рис. 4.74.

Рис. 4.74.Формат регистра состояния контроллера SPI

Регистр SPxSR содержит всего три бита флагов состояния:

SPIF:

Бит завершения обмена одним байтом данных. Устанавливается в момент, когда все восемь бит данных выставлены на линию последовательного обмена. Этот бит сигнализирует микроконтроллеру о том, что записанный ранее байт данных передан в линию и можно либо загружать новый байт для передачи, либо читать принятый в процессе передачи байт. Этот бит сбрасывается в результате выполнения двух последовательных операций. Сначала читают регистр состояния SPxSR, затем выполняют операцию чтения или записи регистра данных SP0DR.

WCOL:

Бит нарушения режима передачи данных. Этот бит устанавливается в 1, если МК пытается записать в регистр данных SPxDR новый байт для передачи в то время, когда предыдущий байт еще находится в процессе передачи.

MODF:

Бит нарушения режима контроллера SPI. Устанавливается, если на линию  ведущего (MSTR = 1) подали сигнал низкого логического уровня. Бит MSTR = 1 назначает режим ведущего для контроллера SPI, а

ведущего (MSTR = 1) подали сигнал низкого логического уровня. Бит MSTR = 1 назначает режим ведущего для контроллера SPI, а  = 0 пытается перевести контроллер в режим ведомого. Такая ситуация является конфликтной, о чем и сигнализирует флаг MODF.

= 0 пытается перевести контроллер в режим ведомого. Такая ситуация является конфликтной, о чем и сигнализирует флаг MODF.

Регистр данных SPCxDR

Формат регистра данных контроллера SPI приведен на рис. 4.75. Особенностью этого регистра является то, что он одновременно является регистром для размещения как передаваемых, так и принимаемых данных. Эта особенность обусловлена рассмотренным ранее принципом обмена по интерфейсу SPI. В процессе обмена регистр данных передающего контроллера (этот контроллер ведущий) и регистр данных принимающего контроллера (этот контроллер ведомый) объединяются в 16-разрядный кольцевой сдвиговый регистр. По прошествии восьми импульсов синхронизации SCK 8-разрядное слово из ведущего контроллера сдвигается в регистр данных ведомого контроллера. При этом 8-разрядное слово регистра данных ведомого перемещается в регистр данных ведущего. Таким образом, независимо от того, желает программист передать данные из ведущего в ведомый или принять данные из ведомого в ведущий, в любом из этих случаев оба устройства одновременно принимают и передают данные. Поэтому до сеанса обмена регистр данных ведущего контроллера содержит подготовленные к передаче данные, а после сеанса обмена этот же регистр содержит принятые данные.

Читать дальше

может быть дополнительно сконфигурирована на ввод или на вывод. Примечания 1–5 на рис 4.73 содержат дополнительную информацию по конфигурированию линий порта S для обслуживания контроллера SPI записи 0 или 1 в соответствующие разряды регистра направления передачи DDRS порта S. Мы рассмотрим эти рекомендации в примере программного обслуживания контроллера SPI (раздел 4.19.4).

может быть дополнительно сконфигурирована на ввод или на вывод. Примечания 1–5 на рис 4.73 содержат дополнительную информацию по конфигурированию линий порта S для обслуживания контроллера SPI записи 0 или 1 в соответствующие разряды регистра направления передачи DDRS порта S. Мы рассмотрим эти рекомендации в примере программного обслуживания контроллера SPI (раздел 4.19.4).