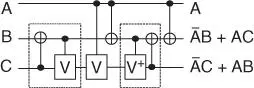

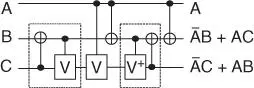

Figure 1.4Quantum realization of reversible Fredkin (FRG) gate.

The cost of all 2  2 gates is the same, and it is 1. For 1

2 gates is the same, and it is 1. For 1  1 gate, the cost is 0. Every circuit can be constructed from those 1

1 gate, the cost is 0. Every circuit can be constructed from those 1  1 and 2

1 and 2  2 quantum primitives, and the cost of circuit is the total sum of required 2

2 quantum primitives, and the cost of circuit is the total sum of required 2  2 gates.

2 gates.

The delay of a logic circuit is the maximum number of gates in a path from any input line to any output line. The definition is based on two assumptions: (i) Each gate performs computation in one unit time and (ii) all inputs to the circuit are available before the computation begins.

The delay of each 1  1 and 2

1 and 2  2 reversible gate is taken as unit delay 1. Any 3

2 reversible gate is taken as unit delay 1. Any 3  3 reversible gate can be designed from 1

3 reversible gate can be designed from 1  1 reversible gates and 2

1 reversible gates and 2  2 reversible gates, such as CNOT gate, controlled‐V, and controlled‐

2 reversible gates, such as CNOT gate, controlled‐V, and controlled‐  gates (V is a square root of NOT gate and

gates (V is a square root of NOT gate and  is its hermitian). Thus, the delay of a 3

is its hermitian). Thus, the delay of a 3  3 reversible gate can be computed by calculating its logical depth when it is designed from smaller 1

3 reversible gate can be computed by calculating its logical depth when it is designed from smaller 1  1 and 2

1 and 2  2 reversible gates.

2 reversible gates.

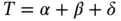

Power of a gate is defined by the energy. Energy of a basic quantum gate is 142.3 meV. Quantum circuits can be implemented with the basic quantum gates and the number of quantum gates depends on the number of basic quantum gates needed to realize it. That means the total number of required quantum gates in the quantum representation of a reversible quantum circuit or gate. So, the power of a reversible gate can be defined as follows: Power = Number of quantum gates  Energy of a basic quantum gate

Energy of a basic quantum gate

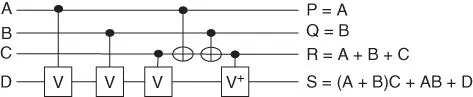

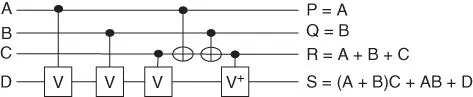

Figure 1.5shows the quantum realization of the reversible HNG gate. From this figures, it is seen that the quantum realization of reversible HNG gate requires total six quantum gates. So, the power of the reversible HNG gate is (6  142.3) meV = 853.8 meV, where the number of quantum gates of HNG circuit is 6.

142.3) meV = 853.8 meV, where the number of quantum gates of HNG circuit is 6.

The area of a reversible gate is defined by the feature size. This size varies according to the number of quantum gates. The size of the basic quantum gates ranges from 50–300 Å. The Angstrom (Å) is a unit equal to  m (one ten‐billionth of a meter), or 0.1 nm. Its symbol is the Swedish letter Å. So, the area of a reversible gate can be defined as follows:

m (one ten‐billionth of a meter), or 0.1 nm. Its symbol is the Swedish letter Å. So, the area of a reversible gate can be defined as follows:

Area = Number of quantum gates  Size of a basic quantum gate

Size of a basic quantum gate

Figure 1.5The quantum representation of reversible HNG gate.

Figure 1.5shows the quantum realization of the reversible HNG gate. From this figures, it is seen that the quantum realization of reversible HNG gate requires total six quantum gates. So, the area of the reversible HNG gate is ((50  6) Å – (300

6) Å – (300  6)Å) = (300 Å – 1800 Å), where the number of quantum gates of HNG circuit is 6.

6)Å) = (300 Å – 1800 Å), where the number of quantum gates of HNG circuit is 6.

The hardware complexity of a reversible logic circuit specifies the total number of Ex‐OR operations, NOT operations, and AND operations used in the circuit. Consequently, the hardware complexity can be determined using the following equation:

(1.10.1)

where

= Hardware complexity (total logical operations)

= A two input EX‐OR gate logical operation

= A two input AND gate logical operation

= A NOT gate logical operation

Figure 1.6shows the block diagram of a reversible Fredkin (FRG) gate. The figure describes that there is only one NOT operation, two EX‐OR operations, and four AND operations. So, the hardware complexity of the reversible FRG gate is  .

.

1.11 Quantum Gate Calculation Complexity

The quantum gate calculation complexity of the quantum representation of a reversible circuit specifies the total number of quantum gates (NOT gates, CNOT gates, and controlled‐V (controlled‐  ) gates) used in the quantum representation of a reversible circuit. Consequently, the quantum gate calculation complexity can be determined using the following equation:

) gates) used in the quantum representation of a reversible circuit. Consequently, the quantum gate calculation complexity can be determined using the following equation:

Читать дальше

2 gates is the same, and it is 1. For 1

2 gates is the same, and it is 1. For 1  1 gate, the cost is 0. Every circuit can be constructed from those 1

1 gate, the cost is 0. Every circuit can be constructed from those 1  1 and 2

1 and 2  2 quantum primitives, and the cost of circuit is the total sum of required 2

2 quantum primitives, and the cost of circuit is the total sum of required 2  2 gates.

2 gates. 1 and 2

1 and 2  2 reversible gate is taken as unit delay 1. Any 3

2 reversible gate is taken as unit delay 1. Any 3  3 reversible gate can be designed from 1

3 reversible gate can be designed from 1  1 reversible gates and 2

1 reversible gates and 2  2 reversible gates, such as CNOT gate, controlled‐V, and controlled‐

2 reversible gates, such as CNOT gate, controlled‐V, and controlled‐  gates (V is a square root of NOT gate and

gates (V is a square root of NOT gate and  is its hermitian). Thus, the delay of a 3

is its hermitian). Thus, the delay of a 3  3 reversible gate can be computed by calculating its logical depth when it is designed from smaller 1

3 reversible gate can be computed by calculating its logical depth when it is designed from smaller 1  1 and 2

1 and 2  2 reversible gates.

2 reversible gates. Energy of a basic quantum gate

Energy of a basic quantum gate 142.3) meV = 853.8 meV, where the number of quantum gates of HNG circuit is 6.

142.3) meV = 853.8 meV, where the number of quantum gates of HNG circuit is 6. m (one ten‐billionth of a meter), or 0.1 nm. Its symbol is the Swedish letter Å. So, the area of a reversible gate can be defined as follows:

m (one ten‐billionth of a meter), or 0.1 nm. Its symbol is the Swedish letter Å. So, the area of a reversible gate can be defined as follows: Size of a basic quantum gate

Size of a basic quantum gate

6) Å – (300

6) Å – (300  6)Å) = (300 Å – 1800 Å), where the number of quantum gates of HNG circuit is 6.

6)Å) = (300 Å – 1800 Å), where the number of quantum gates of HNG circuit is 6.

.

. ) gates) used in the quantum representation of a reversible circuit. Consequently, the quantum gate calculation complexity can be determined using the following equation:

) gates) used in the quantum representation of a reversible circuit. Consequently, the quantum gate calculation complexity can be determined using the following equation: