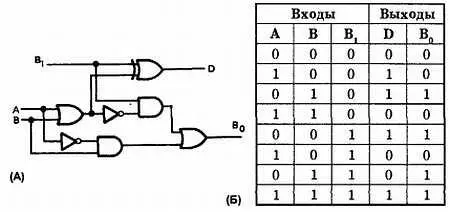

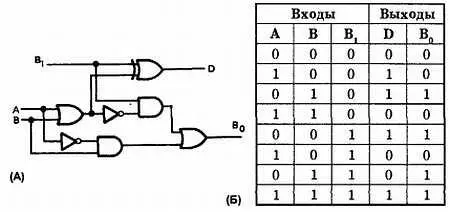

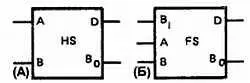

Рис. 35–27. Логическая схема ( А) и таблица истинности ( Б) для полного вычитателя.

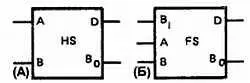

Рис. 35–28. Логические обозначения полу вычитателя ( А) и полного вычитателя ( Б).

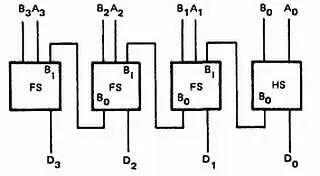

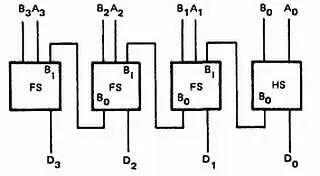

Полный вычитатель может работать только с двумя одноразрядными числами. Для того чтобы вычитать двоичные числа, имеющие большее число разрядов, должны использоваться дополнительные полные вычитатели. Вспомним, что если из 0 вычитать 1, то надо сделать заем из столбца высшего соседнего разряда. Выход заема вычитателя низшего разряда становится входом заема вычитателя высшего соседнего разряда.

На рис. 35–29 изображена блок-схема 4-разрядного вычитателя. В младшем разряде используется полувычитатель, поскольку там не нужен вход заема.

Рис. 35–29. Четырех разрядный вычитатель.

Компаратор

Компаратор используется для сравнения величин двух двоичных чисел. Схема определяет, равны два числа или нет. Компаратор не только сравнивает два двоичных числа, но также определяет какое из них больше, а какое меньше.

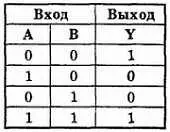

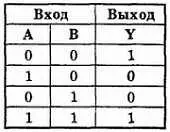

На рис. 35–30 приведена таблица истинности для компаратора.

Рис. 35–30. Таблица истинности для компаратора.

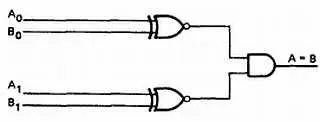

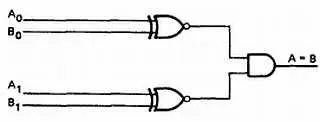

Когда оба сравниваемых бита одинаковы на выходе компаратора появляется высокий уровень. Столбец выхода представляет собой выход элемента исключающее ИЛИ с инверсией, также известное, как исключающее ИЛИ-HE. Элемент исключающее ИЛИ-HE по существу является компаратором, так как на его выходе появляется 1 только тогда, когда на оба входа поданы 1. Для сравнения чисел, имеющих 2 разряда и более необходимы дополнительные элементы исключающее ИЛИ-HE. На рис. 35–31 изображена логическая схема компаратора для сравнения двух 2-разрядных чисел.

Рис. 35–31. Сравнение двух 2-разрядных чисел.

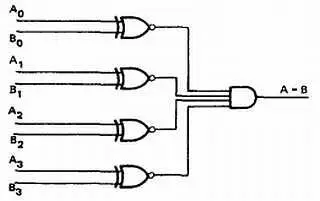

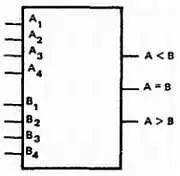

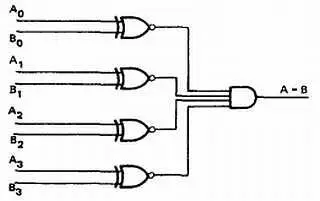

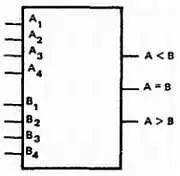

Если числа равны, на выходе элемента исключающее ИЛИ-HE появляется 1. Эта 1 подается на элемент И, как указательный уровень. Если оба элемента исключающее ИЛИ-HE выдают 1 на входы элемента И, то, следовательно, числа равны, и на выходе элемента И также появляется 1. Если же на входах элемента исключающее ИЛИ-HE различные уровни, то элемент исключающее ИЛИ-HE выдает на выходе 0, и на входе элемента И также будет 0. На рис. 35–32 изображена логическая схема компаратора для сравнения двух 4-разрядных чисел. На рис. 35–33 показано обозначение 4-разрядного компаратора.

Рис. 35–32. Сравнение двух 4-разрядных чисел.

Рис. 35–33. Обозначение 4-разрядного компаратора.

35-4. Вопросы

1. Каковы правила сложения двоичных чисел?

2. В чем разница между полусумматором и полным сумматором?

3. Где используется полусумматор?

4. Каковы правила вычитания двоичных чисел?

5. Нарисуйте блок-схему 4-разрядного вычитателя.

6. В чем состоит функция компаратора?

7. Нарисуйте логическую схему компаратора.

РЕЗЮМЕ

• Шифратор имеет один или более входов и создает на выходе многоразрядный двоичный код.

• Десятично-двоичный шифратор преобразует отдельную цифру (от 0 до 9) в четырехразрядный двоичный код, представляющий эту цифру.

• Шифратор с приоритетом выдает код клавиши, соответствующей большей цифре, при одновременном нажатии двух клавиш.

• Десятично-двоичные шифраторы используются для кодировки сигналов от клавиатуры.

• Дешифратор преобразует сложный двоичный код в легко распознаваемые цифры или символы.

• Дешифратор двоично-десятичного кода — это дешифратор специального назначения, предназначенный для управления семисегментными индикаторами.

• Мультиплексор позволяет направлять цифровые данные от отдельных источников в общую линию для передачи по назначению.

Читать дальше