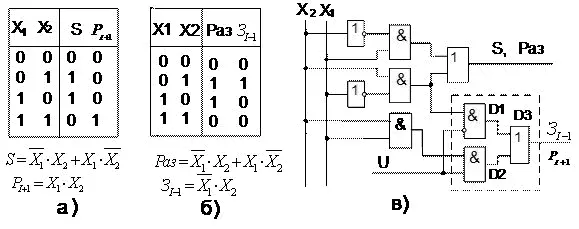

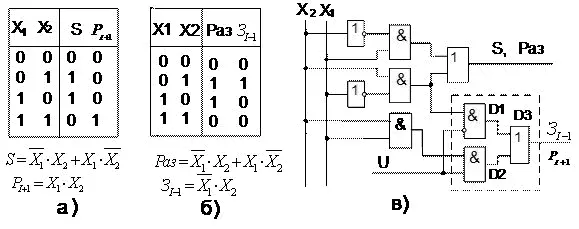

Методика построения одноразрядного арифметического устройства для выполнения операций суммирования и вычитания показана на рисунке 25. Из сравнения логических выражений операций суммирования (Рисунок 25, а) и вычитания (Рисунок 25, б) следует, что выражения для суммы и разности совпадают, а выражение для заёма является частью операции суммирования или вычитания.

Рисунок 25 Таблицы истинности и структурные формулы операции суммирования а), вычитания б) и схема одноразрядного АЛУ в).

Таким образом, для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому и не требуются дополнительные аппаратные затраты. Необходимо лишь обеспечить коммутацию сигналов переноса и заёма в соответствии с кодом операции.

На рисунке 25, в) приведена схема простейшего АЛУ, на которой роль устройства управления выполняют два клапана, управляемые разнополярными сигналами от управляющего напряжения U. Эта часть схемы на рисунке 25,в выделена пунктирной линией. При U=0 выполняется операция вычитания, а при U=1 — операция суммирования.

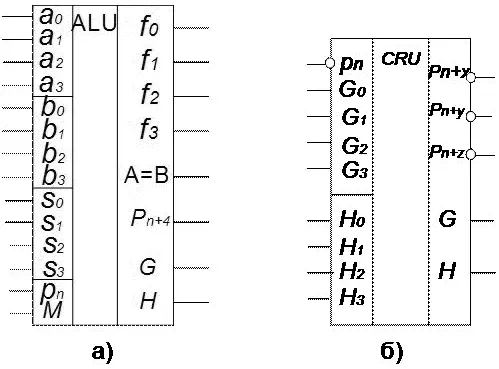

Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их основой.

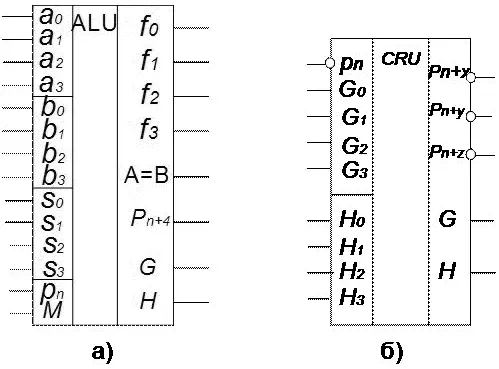

МС 564ИП3 (Рисунок 26,а) — это 4-разрядное параллельное АЛУ, выполняющая 16 арифметических и 16 логических операций.

Рисунок 26 Схема 4-разрядного АЛУ 564ИП3 а) и схема ускоренного переноса 564ИП4 б).

A( а 0–а 3 ) — первый операнд,

B( b 0–b 3 ) — второй операнд,

S( s 0–s 3 ) — код операции — 4 разряда.

Если M=0, то выполняются арифметические операции: 2 4=16, при M=1 выполняются логические операции: 2 4=16. Итого 16+16=32 операции.

F( f 0–f3 ) — результат операции. На выходе A=B появляется «1», если при выполнении операции вычитания результат операции будет равен «0», то есть A=B. Поскольку АЛУ параллельного типа, то имеются выходы генерации G и распространения переноса H . P n и Р n+4 — входной и выходной переносы.

Для увеличения разрядности обрабатываемых слов МС АЛУ можно соединять последовательно, как и в параллельных сумматорах с последовательным переносом. При этом, конечно, увеличивается время выполнения операций.

Уменьшить это время и, следовательно, увеличить быстродействие АЛУ можно применением схемы ускоренного переноса 564ИП4, рисунок 26, б). Используя четыре МС АЛУ и одну МС ускоренного переноса можно получить 16-разрядное полностью параллельное АЛУ, время суммирования которого равно времени суммирования одной микросхемы.

4.2 Кодирующие и декодирующие устройства

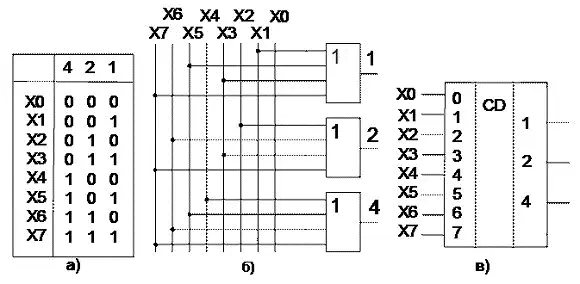

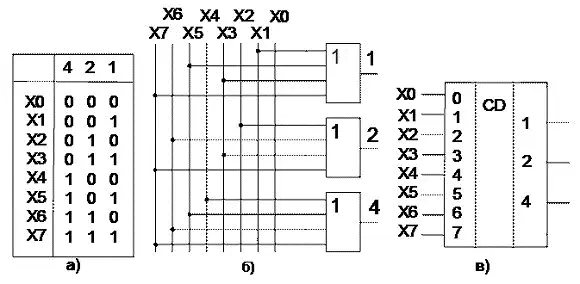

Шифратор (кодер) — это функциональный узел, предназначенный для преобразования поступающих на его входы управляющих сигналов (команд) в n-разрядный двоичный код. В частности, такими сигналами или командами могут быть десятичные числа, например, номер команды, который с помощью шифратора преобразуется в двоичный код.

В качестве примера разработаем схему 3-разрядного шифратора. Вначале следует построить таблицу кодов (таблицу истинности), в которой код номера сигнала представим, например, двоичным кодом (Рисунок 27,а). Схема, реализованная на элементах ИЛИ, приведена на рисунке 27,б.

Рисунок 27 Таблица кодов 3-разрядного шифратора а), его функциональная схема б) и УГО в).

В общем случае, при использовании двоичного кода, можно закодировать 2 nвходных сигналов. В рассмотренной выше схеме выходной код «000» будет присутствовать на выходе при подаче сигнала на вход X0 и в случае, если входной сигнал вообще не подаётся ни на один из входов. Для однозначной идентификации сигнала X0 в интегральных схемах формируется ещё один выходной сигнал — признак подачи входного сигнала, который используется и для других целей.

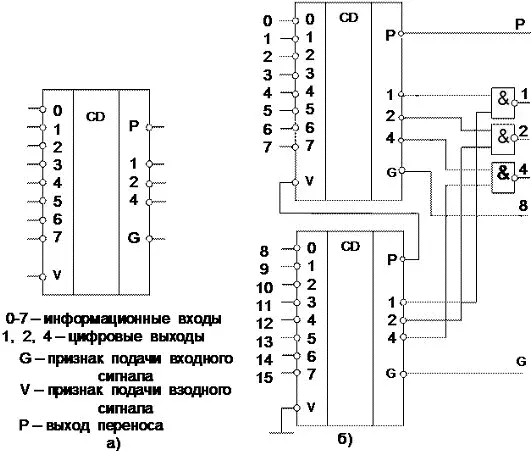

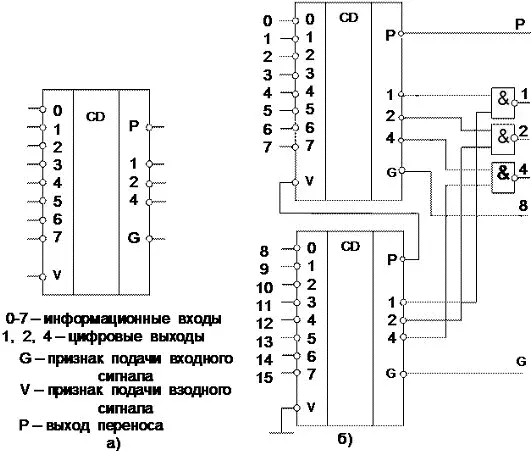

На рисунке 28 приведено УГО схемы 3-х разрядного приоритетного шифратора на 8 входов.

Рисунок 28 3-разрядный приоритетный шифратор К555ИВ1 а) и соединение двух МС б)

При подаче сигнала на любой из входов, устанавливается G=1, P=0, а на цифровых выходах — двоичный код номера входа, на который подан входной сигнал. Если сигнал подан одновременно на два или несколько входов, то на выходе установится код входа с большим номером. Отсюда название шифратора «приоритетный».

Читать дальше

![Стивен Хокинг - Черные дыры. Лекции BBC [litres]](/books/402420/stiven-hoking-chernye-dyry-lekcii-bbc-litres-thumb.webp)