6.1.2. Прямой доступ к памяти — DMA

Прямой доступ к памяти позволяет абоненту шины организовывать обмен данными между своим регистром и памятью под управлением контроллера DMA, минуя центральный процессор. До выполнения обмена канал DMA должен быть инициализирован — задан начальный адрес и размер пересылаемого блока памяти, направление и режим обмена. После инициализации канала обмен выполняется по инициативе ПУ.

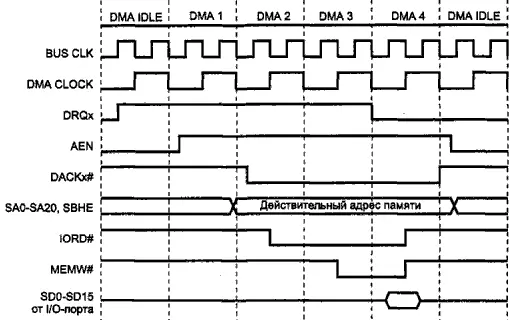

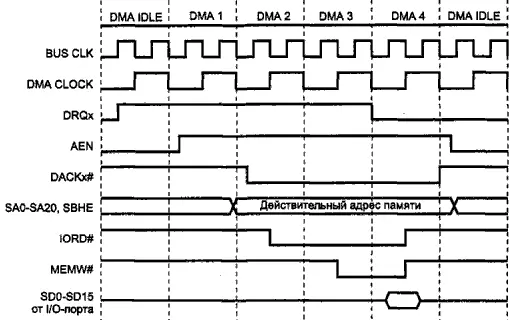

Для интерфейса ПУ каждый канал DMA представляется парой сигналов: запрос обмена — DRQxи подтверждение обмена — DACKx#, где x— номер используемого канала. На рис. 6.3 приведена диаграмма стандартного цикла передачи байта (для 8-битного канала) или слова (для 16-битного) от ПУ в память по каналу DMA. Цикл передачи блока байтов или слов в память будет выглядеть следующим образом.

1. По сигналу DRQxконтроллер DMA запрашивает управление шиной и дожидается его предоставления процессором (и другими контроллерами шины).

2. Контроллер выставляет адрес ячейки памяти и формирует в одном цикле шины сигналы IOR#, DACKx#и MEMW#. Адрес на всех линиях, включая LA[23:17], действителен во время всего цикла (защелкивание не требуется), BALE=H в течение всего цикла. Сигнал DACKx#указывает на то, что операция выполняется для канала x, a IOR#— на направление в канале (для пересылки из памяти в канал использовался бы сигнал IOW#). Чтобы по сигналу IOR#не было ложного чтения (по IOW#— ложной записи) порта, адрес которого совпадает с адресом памяти, присутствующим в цикле DMA, контроллер высоким уровнем сигнала AENзапрещает портам дешифрацию адреса. Байт, считанный из ПУ, в том же цикле шины записывается в ячейку памяти.

3. Контроллер модифицирует счетчик адреса и повторяет шаги 1–2 для каждого следующего сигнала DRQx, пока не будет исчерпан счетчик циклов. В последнем цикле обмена контроллер формирует общий сигнал окончания TC(Terminate Count), который может быть использован устройством для формирования сигнала аппаратного прерывания.

Рис. 6.3. Цикл обмена DMA

Диаграмма обратной пересылки (из памяти в ПУ) отличается только тем, что на месте сигнала IOR#будет сигнал MEMR#, а на месте MEMW#— сигнал IOW#. Направление обмена и параметры режима задаются программированием контроллера DMA.

Цикл DMA, и так довольно длинный, может быть растянут устройством с помощью сигнала IOCHRDY(но сократить его сигналом 0WS#невозможно). Запрашивать удлинение цикла может только адресованная память — подразумевается, что когда ПУ выставляет запрос DRQx, оно уже должно быть готово к обмену.

На 16-битной шине ISA доступно 7 каналов DMA: четыре 8-битных (номера 0–3) и три 16-битных (5–7), подключенные к первичному и вторичному контроллерам соответственно. Канал 4 используется для каскадирования (соединения контроллеров). На 8-битном слоте доступны только четыре 8-битных канала (в XT только 3 — канал 0 требовался для регенерации памяти).

Кроме приведенного на рисунке режима одиночной передачи возможны и иные, описанные в п. 12.4.

Напомним, что по 8-битным каналам DMA за один сеанс настройки контроллера можно передавать не более 64К байт данных, начинающихся с любого адреса (но не пересекая границ страниц, см. п. 12.3.2 и 12.5). По 16-битным каналам за сеанс можно передавать не более 64К слов данных, начинающихся с четного адреса, и границы страниц иные. Используя DMA в режимах, отличных от одиночного, длительность непрерывной передачи не должна превышать 15 мкс (для обеспечения регенерации памяти).

6.1.3. Прямое управление шиной

В случае прямого управления шиной (bus mastering) инициатором обмена становится контроллер какого-либо устройства или интерфейса, но не процессор и не канал DMA. Прямое управление позволяет контроллеру, не отвлекая центральный процессор, выполнять обмен данными с высокой производительностью и, возможно, по более сложным правилам и без ограничений, присущих каналам DMA (невозможность пересечения границы страницы). Контроллер, как правило, обеспечивает обмен данными между системным ОЗУ и своим периферийным устройством или интерфейсом. В принципе он может общаться с памятью или портами другого абонента шины, но для упрощения организации всех информационных связей центральным «перевалочным пунктом» все-таки является системное ОЗУ. Получить право на управление шиной ISA может только контроллер, подключенный к 16- битному слоту. Для арбитража запросов на управление шиной от нескольких источников — центрального процессора, контроллера DMA и контроллеров- абонентов шины используется второй контроллер DMA (каналы 5–7). Устройство, желающее получить управление, выставляет запрос DRQx(x=5…7), по которому контроллер DMA запрашивает управление шиной у центрального процессора. Получив подтверждение от процессора, контроллер устанавливает сигнал AEN(для блокировки дешифрации адреса портов) и формирует сигнал DACKx. Получив этот сигнал, устройство устанавливает низкий уровень на линии MASTER#, по которому контроллер шины DMA снимает сигнал AENи освобождает линии командных сигналов. Таким образом, управление шиной переходит к данному устройству до тех пор, пока оно не снимет запрос DRQx. В режиме прямого управления шиной ISA устройство становится полновластным и бесконтрольным хозяином как самой шины, так и системы в целом (через мост шины). Если шина захватывается более чем на 15 мкс, контроллер устройства должен заботиться о регенерации памяти (см. ниже). Устройства (и память), к которым обращается задатчик шины, могут потребовать введения тактов ожидания сигналом IOCHRDY, и это требование должно удовлетворяться.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)