♦ SD[15:8]— шина данных.

♦ SBHE#— признак наличия данных на линиях SD[15:8].

♦ LA[23:17]— нефиксированные сигналы адреса, требующие защелкивания по спаду сигнала BALE. Такой способ подачи адреса позволяет сократить задержку. Кроме того, схемы дешифратора адреса памяти плат расширения начинают декодирование несколько раньше спада BALE.

♦ IRQ[10:12], IRQ[14:15]— дополнительные запросы прерываний.

♦ DRQ[5:7]— запросы 16-битных каналов DMA (положительным перепадом).

♦ DACK[5:7]#— подтверждение запросов 16-битных каналов DMA.

♦ DRQ0и DACK0#— запрос и подтверждение 8-битного канала DMA, освободившегося от регенерации памяти.

Перечисленные ниже сигналы связаны с переключением разрядности данных.

♦ МEMCS16#( M16#) — адресуемое устройство поддерживает 16-битные обращения к памяти.

♦ IOCS16#( I/OCS16#, IO16#) — адресуемое устройство поддерживает 16-битные обращения к портам.

К новым управляющим сигналам относятся следующие.

♦ MEMW#( MWTC#) — запись в память в любой области до 16 Мбайт.

♦ MEMR#( MRDC#) — чтение памяти в любой области до 16 Мбайт.

♦ OWS#( SRDY#, NOWS#, ENDXFR) — укорочение текущего цикла по инициативе адресованного устройства.

♦ MASTER#( MASTER16#) — запрос от устройства, использующего 16-битный канал DMA на управление шиной. При получении подтверждения DACK[5:7]Bus-Master может захватить шину.

В шине EISA на дополнительных контактах слотов (недоступных картам ISA) располагается расширение шин данных и адреса до 32 бит, а также набор сигналов, обеспечивающих передачу данных в синхронном режиме с возможностью пакетных циклов.

6.1.1. Обычная передача данных

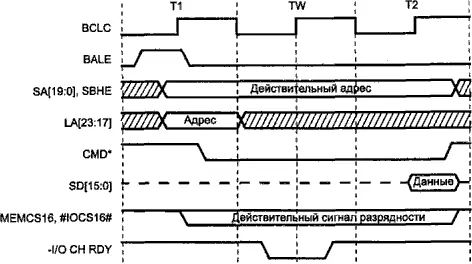

Для передачи данных от исполнителя к задатчику предназначены циклы чтения ячейки памяти или порта ввода-вывода, для передачи данных от задатчика к исполнителю — циклы записи ячейки памяти или порта ввода-вывода. В каждом цикле текущий (на время данного цикла) задатчик формирует адрес обращения и управляющие сигналы, а в циклах записи еще и данные на шине. Адресуемое устройство-исполнитель в соответствии с полученными управляющими сигналами принимает (в цикле записи) или формирует (в цикле чтения) данные. Также оно может, при необходимости, управлять длительностью цикла и разрядностью передачи. Обобщенные временные диаграммы циклов чтения или записи памяти или ввода-вывода приведены на рис. 6.2. Здесь условный сигнал CMD* изображает один из следующих сигналов:

♦ SMEMR#, MEMR#— в цикле чтения памяти;

♦ SMEMW#, MEMW#— в цикле записи памяти;

♦ IOR#— в цикле чтения порта ввода-вывода;

♦ IOW#— в цикле записи порта ввода-вывода.

Рис. 6.2. Временные диаграммы циклов чтения или записи на шине ISA

В каждом из рассматриваемых циклов активными (с низким уровнем) могут быть только сигналы лишь из одной строки данного списка, и во время всего цикла сигнал AENимеет низкий уровень. Цикл прямого доступа к памяти, в котором это правило не соблюдается, рассмотрен ниже, и в таком цикле сигнал AENбудет иметь высокий уровень. Сигналы SMEMR#и SMEMW#вырабатываются из сигналов MEMR#и MEMW#соответственно, когда адрес принадлежит диапазону 0-FFFFFh. Поэтому сигналы SMEMR#и SMEMW#задержаны относительно MEMR#и MEMW#на 5-10 нс.

В начале каждого цикла контроллер шины устанавливает адрес обращения: на линиях SA[19:0]и SBHE#действительный адрес сохраняется на время всего текущего цикла; на линиях LA[23:17]адрес действителен только в начале цикла, так что требуется его «защелкивание». Каждое устройство имеет дешифратор адреса — комбинационную схему, срабатывающую только тогда, когда на шине присутствует адрес, относящийся к данному устройству. В фазе адресации устройства еще «не знают», к какому из пространств (памяти или ввода-вывода) относится выставленный адрес. Но дешифраторы адресов уже срабатывают, и, когда в следующей фазе шина управления сообщает тип операции, адресуемое устройство уже оказывается готовым к ее исполнению. Если устройство использует линии LA[23:17](они нужны лишь для обращений к памяти выше границы FFFFFh), то они на дешифратор адреса должны проходить через регистр-защелку, «прозрачный» во время действия сигнала BALEи фиксирующий состояние выходов по его спаду. Это позволяет дешифратору, всегда вносящему некоторую задержку, начинать работу раньше, чем поступит управляющий сигнал чтения или записи. При обращении к портам ввода-вывода сигналы LA[32:17]не используются.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)