Регистр ВРRимеет длину в один бит. Он используется как кратчайший обходной путь для последовательных данных, когда остальные регистры не участвуют в обмене.

Регистр BSRпредставляет собой длинный сдвигающий регистр, каждым битом которого являются пограничные ячейки, установленные на всех входных и выходных сигналах процессора. Для двунаправленных сигналов (или их групп), кроме собственно информационных ячеек регистра, соответствующих внешним сигналам, имеются и управляющие ячейки, задающие режим работы информационных ячеек. К примеру, у процессоров P6 длина BSRсоставляет 159 бит.

Регистр DIDдлиной 32 бита содержит идентификатор производителя, код устройства и номер версии, по которым TAP-контроллер может распознать, с каким устройством он имеет дело.

Регистр IRслужит для хранения исполняемой тестовой инструкции. Его длина зависит от тестируемого устройства. Для всех устройств обязательными являются инструкции BYPASS, IDCODE, SAMPLEи EXTEST.

Инструкция BYPASS(все биты кода — единичные) предназначена для подключения однобитного обходного регистра, обеспечивая скорейшее прохождение данных через устройство; при этом оно никак не реагирует на проходящий поток. Вход TDIобычно «подтягивают» резистором к высокому уровню, при этом разрыв цепочки JTAG приведет к подключению обходных регистров во всех устройствах после точки обрыва. Это исключает возможные непредсказуемые действия устройств в случае обрыва.

Инструкция идентификации IDCODE(младшие биты кода — 10) подключает к интерфейсу регистр DID, позволяя считать его содержимое (поступающие входные данные не могут изменить его значение).

Инструкция SAMPLE/PRELOAD(младшие биты кода — 01) имеет два назначения. Когда TAP-контроллер находится в состоянии Capture-DR (см. ниже), эта инструкция позволяет выполнить моментальный «снимок» состояния всех внешних сигналов без воздействия на работу устройства. Значение сигналов фиксируется по положительному перепаду TCK. В состоянии Update-DR по этой инструкции данные загружаются в выходные ячейки тестового порта (но еще не на выходы устройства), откуда впоследствии они будут выводиться (подаваться на выводы процессора) по инструкции EXTEST. Данные загружаются по спаду сигнала TCK.

Инструкция EXTEST(младшие биты кода — 00) предназначена для проверки внешних цепей (по отношению к тестируемому устройству). При этом на выходные выводы подаются сигналы, предварительно записанные в регистр BSR, а состояние входных сигналов фиксируется в этих регистрах. Двунаправленные сигналы предварительно конфигурируются соответствующими им управляющими битами ячеек BSR.

Стандарт 1149.1 предусматривает и инструкцию тестирования внутренней логики устройства INTEST, но ее поддерживают не все устройства.

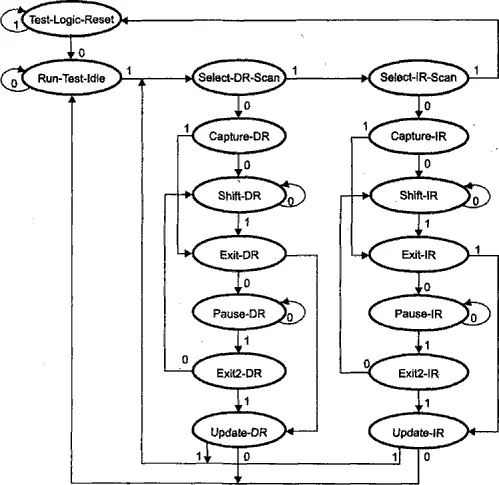

Контроллер тестового порта (TAP-controller) представляет собой синхронный конечный автомат, изменяющий состояние по фронту сигнала TCKи по включению питания. Сменой состояний управляет сигнал TMS(Test Mode State), воспринимаемый по положительному перепаду TCK. Граф состояний и переходов управляющего автомата представлен на рис. 11.8. Около стрелок переходов указаны значения сигнала TMSво время фронта TCK.

Рис. 11.8. Граф состояний и переходов контроллера TAP

В исходное состояние Test-Logic-Reset контроллер автоматически переходит по включении питания и из любого другого состояния может быть переведен высоким уровнем TMS, удерживаемым не менее пяти тактов TCK. Для перевода в состояние Test-Logic-Reset иногда используют и дополнительный сигнал TRST. В этом состоянии тестовая логика запрещена, и устройство работает в нормальном режиме.

Состояние Run-Test/Idle является промежуточным между выполнением тестовых операций. В этом состоянии регистры не изменяют своего значения.

В состоянии Capture-DR во время выполнения инструкций EXTESTи SAMPLE/PRELOADсканирующий регистр фиксирует только данные на входных линиях.

В состоянии Shift-DR данные с TDIпродвигаются через подключенный сдвиговый регистр на выход TDO.

В состоянии Pause-DR контроллер временно запрещает продвижение данных через сдвиговый регистр.

В состоянии Update-DR по спаду TCKсигналы из сдвигового регистра фиксируются на выходах тестовых ячеек.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)