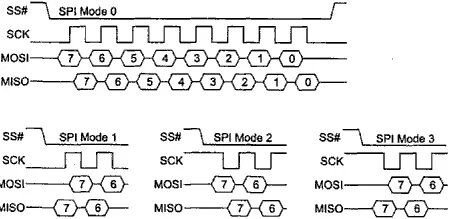

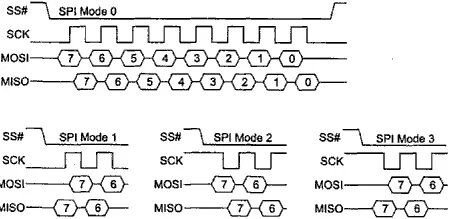

Рис. 11.5. Форматы передач по интерфейсу SPI

Интерфейс JTAG (Joint Test Action Group) предназначен для тестирования сложных логических схем, установленных в целевое устройство. Этот интерфейс описан в стандарте IEEE 1149.1 Boundary Scan Architecture и является последовательным синхронным, но в связи со спецификой назначения значительно отличается от вышеописанных интерфейсов, ориентированных на передачу данных. Интерфейсом JTAG управляет одно устройство-контроллер (чаще всего это ПК с соответствующим интерфейсным адаптером), к которому может быть подключено несколько тестируемых устройств. Ниже перечислены сигналы интерфейса JTAG.

♦ TCK(Test Clock) — сигнал синхронизации последовательных данных; генерируется контроллером. Частота синхронизации может достигать 16 МГц.

♦ TMS(Test Mode Select) — сигнал выбора тестового режима. Генерируется контроллером.

♦ TDI(Test Data Input) — входные данные, принимаемые устройством в последовательном двоичном коде (младшим битом вперед).

♦ TDO(Test Data Output) — выходные данные, передаваемые устройством в последовательном двоичном коде.

♦ TRST(Test Logic Reset) — необязательный сигнал сброса логики интерфейсного порта, генерируемый контроллером.

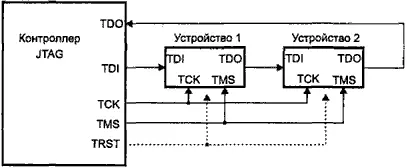

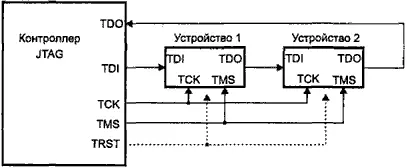

Эти сигналы (все однонаправленные), имеющие обычные логические уровни, образуют тестовый порт TAP (Test Access Port), через который тестируемое устройство подключается к тестирующему оборудованию (контроллеру). В задачу тестирующего оборудования входит формирование тестовых сигналов по программе тестирования, определенной разработчиком тестируемого устройства, и сравнение полученных результатов с эталонами. Один и тот же контроллер и порт могут использоваться для тестирования любого числа устройств, поддерживающих JTAG. Для этого устройства своими портами TAP соединяются в цепочку (рис. 11.6). Стандартизованный логический формат позволяет контроллеру независимо общаться с каждым из устройств цепочки (для этого, конечно, они должны иметь исправные ячейки JTAG).

Рис. 11.6. Цепочка устройств с интерфейсом JTAG

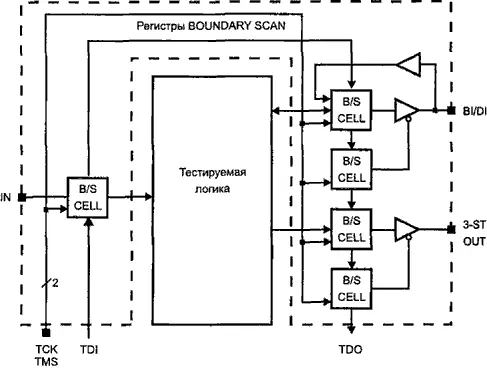

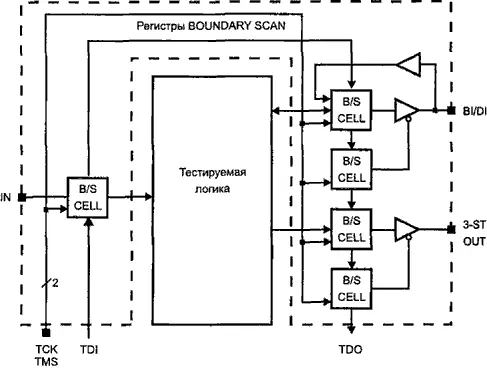

Идею тестирования любой цифровой схемы иллюстрирует рис. 11.7, на котором показана условная цифровая система, имеющая входные, выходные (возможно, с третьим состоянием) и двунаправленные сигналы. Ячейки тестирования B/S врезаются между реальными внешними выводами устройства и собственно логическим устройством, то есть располагаются на логической границе (boundary) устройства. TAP-контроллер способен сканировать ячейки — управлять ими и считывать с них информацию. Отсюда и пошло название Boundary Scan , которое можно перевести как «периферийное сканирование». При включенном тестовом режиме TAP-контроллер может логически отсоединить сигналы от внешних выводов, задавать входные воздействия и считывать результаты — собственно, это все, что необходимо для тестирования последовательностных схем (автоматов с памятью). Прелесть JTAG заключается в том, что независимо от сложности устройства оно тестируется с помощью всего лишь четырех сигналов — все сложности прячутся в достаточно простые ячейки, «окутывающие» его сигнальные выводы.

Рис. 11.7. Включение ячеек сканирования

Тестовая логика, встраиваемая в устройство, поддерживающее JTAG, состоит из следующих элементов:

♦ тестовый порт TAP (четыре интерфейсных сигнала);

♦ TAP-контроллер, управляющий тестовыми регистрами;

♦ регистр инструкций IR (Instruction Register), который принимает последовательный код со входа TDI (код инструкции используется для выбора исполняемой тестовой операции или регистра тестовых данных, к которым производится обращение);

♦ регистры тестовых данных, из которых любое устройство должно иметь три обязательных регистра: ВPR(Bypass Register), DID(Device Identification Register) и BSR(Boundary Scan Register).

Регистры инструкций и данных представляют собой независимые сдвиговые регистры, соединенные параллельно. На их входы (старшие биты) приходит сигнал TDI, с выходов (младшие биты) снимается сигнал TDO. По каждому положительному перепаду данные продвигаются на один бит.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)