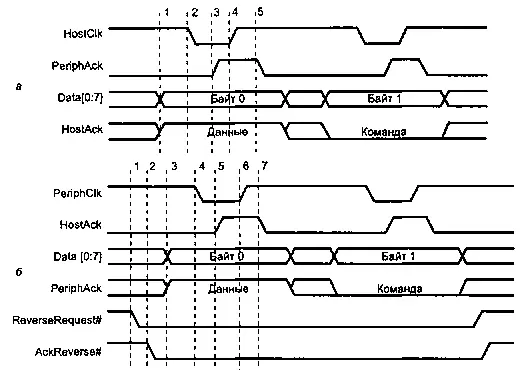

Рис. 1.5. Передача в режиме ECP: а — прямая, б — обратная

В отличие от диаграмм обмена EPP, на рис. 1.5 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO-буфер. Обмен драйвера с FIFO-буфером может осуществляться как с использованием DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ECP. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но обычно важно только то, завершен он или нет.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

1. Хост помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии HostAck.

2. Хост устанавливает низкий уровень на линии HostClk, указывая на действительность данных.

3. ПУ отвечает установкой высокого уровня на линии PeriphAck.

4. Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

5. ПУ устанавливает низкий уровень на линии PeriphAckдля указания на готовность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClkпереходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

Из рис. 1.5 видно и другое отличие ЕСР от EPP. Протокол EPP позволяет драйверу чередовать циклы прямой и обратной передачи, не запрашивая подтверждения на смену направления. В ЕСР смена направления должна быть согласована: хост запрашивает реверс установкой ReverseRequest#, после чего он должен дождаться подтверждения сигналом AckReverse#. Поскольку предыдущий цикл мог выполняться по прямому доступу, драйвер должен дождаться завершения прямого доступа или прервать его, выгрузить буфер FIFO, определив точное значение счетчика переданных байт, и только после этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

1. Хост запрашивает изменение направления канала, устанавливая низкий уровень на линии ReverseRequest#.

2. ПУ разрешает смену направления установкой низкого уровня на линии AckReverse#.

3. ПУ помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии PeriphAck.

4. ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действительность данных.

5. Хост отвечает установкой высокого уровня на линии HostAck.

6. ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может использоваться для фиксации данных хостом.

7. Хост устанавливает низкий уровень на линии HostAckдля указания на готовность к приему следующего байта.

1.3.5. Режимы и регистры ЕСР-порта

Программный интерфейс и регистры ЕСР для адаптеров IEEE 1284 определяет спецификация Microsoft. Порт ЕСР может работать в различных режимах, приведенных в табл. 1.7, где код соответствует полю Modeрегистра ECR(биты [7:5]).

Таблица 1.7. Режимы ЕСР-порта

| Код |

Режим |

| 000 |

SPP mode , стандартный (традиционный) режим |

| 001 |

Bi-directional mode , двунаправленный порт (тип 1 для PS/2) |

| 010 |

Fast Centronics , однонаправленный с использованием FIFO и DMA |

| 011 |

ЕСР Parallel Port mode , собственно режим ЕСР |

| 100 |

ЕРР Parallel Port mode , режим ЕРР¹ |

| 101 |

Зарезервировано |

| 110 |

Test mode , тестирование работы FIFO и прерываний |

| 111 |

Configuration mode , доступ к конфигурационным регистрам |

¹ Этот режим не входит в спецификацию Microsoft, но трактуется как ЕРР многими адаптерами портов, если в CMOS Setup установлен режим ЕСР+ЕРР.

Регистровая модель адаптера ЕСР (табл. 1.8) использует свойства архитектуры стандартной шины и адаптеров ISA, где для дешифрации адресов портов ввода-вывода задействуются только 10 младших линий шины адреса. Поэтому, например, обращения по адресам Port, Port+400h, Port+800h… будут восприниматься как обращения к адресу Port, лежащему в диапазоне 0-3FFh. Современные PC и адаптеры декодируют большее количество адресных бит, поэтому обращения по адресам 0378h и 0778Н будут адресованы двум различным регистрам. Помещение дополнительных регистров ЕСР «за спину» регистров стандартного порта (смещение 400-402Н) преследует две цели. Во-первых, эти адреса никогда не использовались традиционными адаптерами и их драйверами, и их применение в ЕСР не приведет к сужению доступного адресного пространства ввода-вывода. Во-вторых, этим обеспечивается совместимость со старыми адаптерами на уровне режимов 000–001 и возможность определения факта присутствия ЕСР-адаптера посредством обращения к его расширенным регистрам.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)