2. Адаптер устанавливает сигнал Write#(низкий уровень), и данные помещаются на выходную шину LPT-порта.

3. При низком уровне Wait#устанавливается строб данных.

4. Порт ждет подтверждения от ПУ (перевода Wait#в высокий уровень).

5. Снимается строб данных — внешний EPP-цикл завершается.

6. Завершается процессорный цикл вывода.

7. ПУ устанавливает низкий уровень Wait#, указывая на возможность начала следующего цикла.

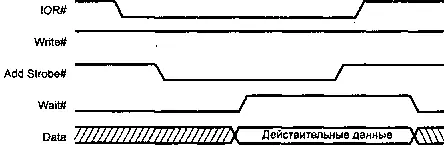

Пример адресного цикла чтения приведен на рис. 1.4. Цикл чтения данных отличается только применением другого стробирующего сигнала.

Рис. 1.4. Адресный цикл чтения EPP

Главной отличительной чертой EPP является выполнение внешней передачи во время одного процессорного цикла ввода-вывода. Это позволяет достигать высоких скоростей обмена (0,5–2 Мбайт/с). ПУ, подключенное к параллельному порту EPP, может работать со скоростью устройства, подключаемого через слот ISA.

Протокол блокированного квитирования (interlocked handshakes) позволяет автоматически настраиваться на скорость обмена, доступную и хосту, и ПУ. ПУ может регулировать длительность всех фаз обмена с помощью всего лишь одного сигнала Wait#. Протокол автоматически подстраивается под длину кабеля — вносимые задержки приведут только к удлинению цикла. Поскольку кабели, соответствующие стандарту IEEE 1284 (см. выше), имеют одинаковые волновые свойства для разных линий, нарушения передачи, связанного с «состязаниями» сигналов, происходить не должно. При подключении сетевых адаптеров или внешних дисков к EPP-порту можно наблюдать непривычное явление: снижение производительности по мере удлинения интерфейсного кабеля.

Естественно, ПУ не должно «подвешивать» процессор на шинном цикле обмена. Это гарантирует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс. В ряде реализаций EPP за тайм-аутом интерфейса следит сам адаптер — если ПУ не отвечает в течение определенного времени (5 мкс), цикл прекращается и в дополнительном (нестандартизованном) регистре состояния адаптера фиксируется ошибка.

Устройства с интерфейсом EPP, разработанные до принятия IEEE 1284, отличаются началом цикла: строб DataStb#или AddrStb# устанавливается независимо от состояния WAIT#. Это означает, что ПУ не может задержать начало следующего цикла (хотя может растянуть его на требуемое время). Такая спецификация называется EPP 1.7 (предложена Xircom). Именно она применялась в контроллере 82360. Периферия, совместимая с IEEE 1284 EPP, будет нормально работать с контроллером EPP 1.7, но ПУ в стандарте EPP 1.7 может отказаться работать с контроллером EPP 1284.

С программной точки зрения контроллер EPP-порта выглядит просто (см. табл. 1.5). К трем регистрам стандартного порта, имеющим смещение 0, 1 и 2 относительно базового адреса порта, добавлены два регистра ( EPP Address Portи EPP Data Port), чтение и запись в которые вызывает генерацию связанных внешних циклов.

Назначение регистров стандартного порта сохранено для совместимости EPP-порта с ПУ и ПО, рассчитанными на применение программно-управляемого обмена. Поскольку сигналы квитирования адаптером вырабатываются аппаратно, при записи в регистр управления CR биты 0, 1 и 3, соответствующие сигналам Strobe#, AutoFeed#и SelectIn#должны иметь нулевые значения. Программное вмешательство могло бы нарушить последовательность квитирования. Некоторые адаптеры имеют специальные средства защиты ( EPP Protect ), при включении которых программная модификация этих бит блокируется.

Использование регистра данных EPP позволяет осуществлять передачу блока данных с помощью одной инструкции REP INSBили REP OUTSB. Некоторые адаптеры допускают 16/32-битное обращение к регистру данных EPP. При этом адаптер просто дешифрует адрес со смещением в диапазоне 4–7 как адрес регистра данных EPP, но процессору сообщает о разрядности 8 бит. Тогда 16- или 32-битное обращение по адресу регистра данных EPP приведет к автоматической генерации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выполняться быстрее, чем то же количество одиночных циклов. Более «продвинутые» адаптеры для адреса регистра данных EPP сообщают разрядность 32 бит и для них до 4 байт может быть передано за один цикл обращения процессора. Таким образом обеспечивается производительность до 2 Мбайт/с, достаточная для адаптеров локальных сетей, внешних дисков, стриммеров и CD-ROM. Адресные циклы EPP всегда выполняются только в однобайтном режиме.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)