Интересно решение построения интерфейса PCI на конфигурируемой логике FPGA (Field Programmable Gate Array — программируемый массив вентилей). Здесь PCI-ядро, а также функции целевого и ведущего устройств занимают 10–15 тысяч вентилей в зависимости от требуемых функций (см. www.xilink.com, www.altera.com). Микросхемы FPGA выпускаются на 20, 30 и 40 тысяч вентилей — оставшаяся часть может быть использована для реализации функциональной части устройства, буферов FIFO и т.п.

Быстро перевести разработки с шиной ISA на PCI можно с помощью микросхем-мостов PCI–ISA (см., например, www.iss-us.com).

6.3. Магистральный интерфейс AGP

В настоящее время самой быстрой универсальной шиной расширения является PCI, имеющая при тактовой частоте 66 МГц и разрядности 32 бит пиковую пропускную способность 264 Мбайт/с. Одним из главных потребителей пропускной способности шины является графический адаптер. По мере увеличения разрешения и глубины цвета требования к пропускной способности шины, связывающей дисплейный адаптер с памятью и центральным процессором компьютера, повышаются. Одно из решений состоит в уменьшении потока графических данных, передаваемых по шине. Для этого графические платы снабжают ускорителями и увеличивают объем видеопамяти, которой пользуется ускоритель при выполнении построений. В результате поток данных в основном циркулирует внутри графической карты, слабо нагружая внешнюю шину. Однако при трехмерных построениях ускорителю становится тесно в ограниченном объеме локальной памяти графического адаптера, и его поток данных снова «выплескивается» на внешнюю шину.

Фирма Intel на базе шины PCI 2.1 разработала стандарт подключения графических адаптеров — AGP (Accelerated Graphic Port — ускоренный графический порт). Первая версия стандарта вышла в 1996 году, в настоящее время действует версия 2.0 (1998 года), отличающаяся от первой в основном введением нового режима передачи 4x. В конце 2000 г. Intel опубликовала проект спецификации AGP8X, которая рассматривается как отдельная спецификация, а не просто развитие предыдущих. Ее особенности отметим в конце раздела.

Порт AGP представляет собой 32-разрядную шину с тактовой частотой 66 МГц, большая часть сигналов позаимствована из шины PCI. Однако в отличие от PCI, порт AGP представляет собой двухточечный интерфейс, соединяющий графический адаптер с памятью и системной шиной процессора напрямую логикой и каналами данных чипсета системной платы, не пересекаясь с «узким местом» — шиной PCI. Поначалу планировался переход на тактовую частоту 100 МГц, но и в спецификации AGP 2.0, и в предлагаемом варианте AGP8X фигурирует лишь одна частота — 66,6 МГц (нынешний предел и для шины PCI). «Ускоренность» порта обеспечивается следующими факторами:

♦ конвейеризацией обращений к памяти;

♦ удвоенной (2х) или учетверенной (4х) частотой передачи данных (относительно тактовой частоты порта);

♦ демультиплексированием шин адреса и данных.

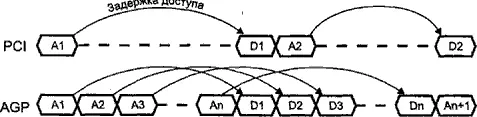

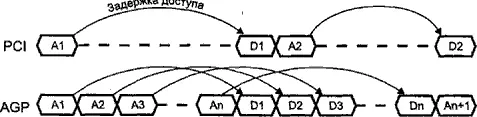

Идею конвейеризации обращений к памяти иллюстрирует рис. 6.11, где сравниваются обращения к памяти PCI и AGP. В PCI во время реакции памяти на запрос шина простаивает (но не свободна). Конвейерный доступ AGP позволяет в это время передавать следующие запросы, а потом получить поток ответов.

Рис. 6.11. Циклы обращения к памяти PCI и AGP

Удвоение и учетверение частоты передачи данных обеспечивает при частоте 66 МГц пропускную способность до 533 (2х) и 1066 Мбайт/с (4х), что для 32-битной шины несколько неожиданно. В этих режимах блоки данных передаются как по фронту, так и по спаду стробирующего сигнала (как в ATA Ultra DMA). Режимы 2х и 4х могут использоваться, лишь если их поддерживают и графический адаптер, и системная плата.

Демультиплексирование (разделение) шины адреса и данных сделано несколько необычным образом. С целью экономии числа интерфейсных линий шину адреса и команды в демультиплексированном режиме AGP представляют всего 8 линий SBA (SideBand Address), по которым команда, адрес и значение длины передачи передаются последовательно за несколько тактов. Поддержка демультиплексированной адресации не является обязательной для устройства AGP, поскольку имеется альтернативный способ подачи адреса по шине AD.

Порт AGP предназначен только для интеллектуального графического адаптера, имеющего SD-ускоритель (для краткости здесь этот адаптер будем называть просто ускорителем). Системная логика порта AGP отличается сложным контроллером памяти, который выполняет глубокую буферизацию и высокопроизводительное обслуживание запросов AGP (от адаптера) и других своих клиентов — центрального процессора (одного или нескольких) и шины PCI. AGP может реализовать всю пропускную способность 64-битной системы памяти компьютера на процессорах Pentium и выше. При этом возможны конкурирующие обращения к памяти как со стороны процессора, так и со стороны мостов шин PCI. Фирма Intel ввела поддержку AGP в чипсеты для процессоров P6, однако нет «противопоказаний» для применения AGP и с Pentium.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)