Отметим, что многие преимущества AGP носят потенциальный характер и могут быть реализованы лишь при поддержке аппаратных средств графического адаптера и ПО. Графический адаптер с интерфейсом AGP может реально вести себя по-разному:

♦ не задействовать конвейеризацию, а использовать только быструю запись PCI (Fast Write);

♦ не работать с текстурами, расположенными в системной памяти, но использовать более быстрый обмен данными между памятью и локальным буфером;

♦ использовать оптимальное распределение текстур между локальной и систем ной памятью, избегая конфликтов с обращениями к памяти от процессора.

Порт AGP содержит практически полный набор сигналов шины PCI и дополнительные сигналы AGP. Устройство, подключаемое к порту AGP, может предназначаться как исключительно для операций AGP, так и быть комбинацией AGP+PCI. Устройство обязательно должно выполнять функции ведущего устройства AGP (иначе порт AGP для него теряет смысл) и функции ведомого устройства PCI со всеми его атрибутами (конфигурационными регистрами и т.п.); дополнительно оно может быть и ведущим устройством PCI. Для транзакций в режиме AGP ему доступно только системное ОЗУ. В режиме PCI обращения возможны как к пространству памяти, так и к пространству ввода-вывода и конфигурационному пространству.

Транзакции в режиме PCI , инициируемые ускорителем, начинаются с подачи сигнала FRAME#и выполняются обычным для PCI способом (см. п. 6.2). Заметим, что при этом на все время транзакции шина AD занята, причем транзакции чтения памяти занимают шину на большее число тактов, чем транзакции записи, — после подачи адреса неизбежны такты ожидания на время доступа к памяти. Запись на шине происходит быстрее — данные записи задатчик посылает сразу за адресом, а на время доступа к памяти они «оседают» в буфере контроллера памяти. Контроллер памяти позволяет завершить транзакцию и освободить шину до физической записи в память. Обращения со стороны процессора (или задатчиков шины PCI) отрабатываются адаптером так же, как обычным устройством PCI.

Конвейерные транзакции AGP (команды AGP) инициируются только ускорителем; логикой AGP они ставятся в очереди на обслуживание и исполняются в зависимости от приоритета, порядка поступления запросов и готовности данных. Эти транзакции могут быть адресованы ускорителем только к системному ОЗУ. Если устройству AGP требуется обратиться к локальной памяти каких-либо устройств PCI, то оно должно выполнять эти транзакции в режиме PCI. Транзакции, адресованные к устройству AGP, отрабатываются им как ведомым устройством PCI, однако имеется возможность быстрой записи в локальную память FW (Fast Write), в которой данные передаются на скорости AGP (2х или 4х), и управление потоком их передач ближе к протоколу AGP, нежели PCI. Транзакции FW обычно инициируются процессором и предназначены для принудительного «заталкивания» данных в локальную память ускорителя.

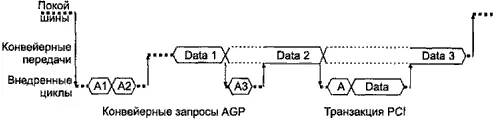

Концепцию конвейера AGP иллюстрирует рис. 6.12. Порт AGP может находиться в одном из четырех состояний:

♦ IDLE — покой;

♦ DATA — передача данных конвейеризированных транзакций;

♦ AGP — постановка в очередь команды AGP;

♦ PCI — выполнение транзакции в режиме PCI.

Рис. 6.12. Конвейер AGP

Из состояния покоя IDLE порт может вывести запрос транзакции PCI (как от ускорителя, так и с системной стороны) или запрос AGP (только от ускорителя). В состоянии PCI транзакция PCI выполняется целиком, от подачи адреса и команды до завершения передачи данных. В состоянии AGP ведущее устройство передает только команду и адрес для транзакции (по сигналу PIPE#или через порт SBA), ставящейся в очередь ; несколько запросов могут следовать сразу друг за другом. В состояние DATA порт переходит, когда у него в очереди имеется необслуженная команда, готовая к исполнению. В этом состоянии происходит передача данных для команд, стоящих в очереди. Это состояние может прерываться запросами PCI (для выполнения целой транзакции) ил и AGP (для постановки в очередь новой команды), но прерывание возможно только на границах данных транзакций AGP. Когда порт AGP обслужит все команды, он снова переходит в состояние покоя. Все переходы происходят под управлением арбитра порта AGP, реагирующего на поступающие запросы (REQ# от ускорителя и внешние обращения от процессора или других устройств PCI) и ответы контроллера памяти.

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)