Конфигурационное пространство устройства начинается со стандартного заголовка, в котором содержатся идентификаторы производителя, устройства и его класса, а также описание требуемых и занимаемых системных ресурсов. После заголовка могут располагаться регистры, специфичные для устройства; они могут занимать адреса конфигурационного пространства в пределах 40-FFh.

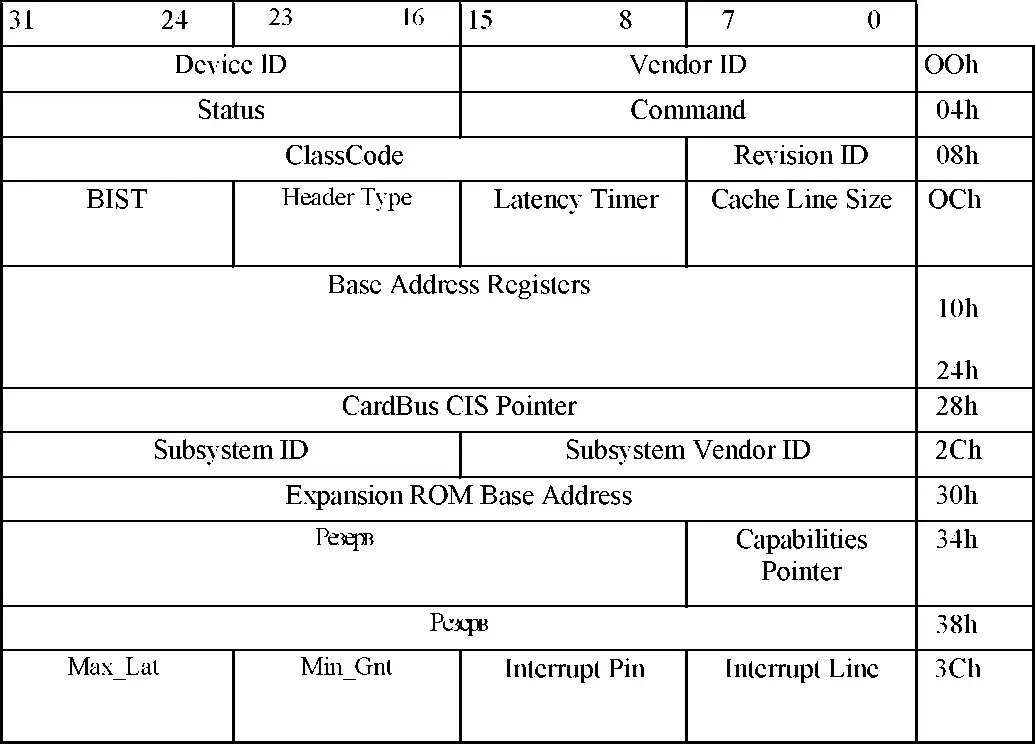

Формат заголовка приведен на рис. 6.10. Серым цветом здесь выделены поля, обязательные для всех устройств.

Рис. 6.10. Формат заголовка конфигурационного пространства устройства PCI

Перечисленные ниже поля идентификации допускают только чтение.

♦ Deviсе ID— идентификатор устройства, назначаемый производителем.

♦ Vendor ID— идентификатор производителя микросхемы PCI, назначенный PCI SIG. Идентификатор FFFFh является недопустимым; это значение должно возвращаться при чтении конфигурационного пространства несуществующего устройства.

♦ Revision ID— версия продукта, назначенная производителем. Используется как расширение поля Device ID.

♦ Header Type— тип заголовка (биты 6:0), определяющий формат ячеек в диапазоне 10-3Fh и несущий признак многофункционального устройства (если бит 7=1). На рисунке приведен формат заголовка типа 0, относящийся именно к устройствам PCI. Тип 01 относится к мостам PCI-PCI; тип 02 относится к мостам для CardBus.

♦ Class Code— код класса, определяющий основную функцию устройства, а иногда и его программный интерфейс (см. п. 6.2.13). Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

Остальные поля заголовка являются регистрами устройств , допускающими как запись, так и чтение.

♦ Command(RW) — регистр команд, управляющий поведением устройства на шине PCI. Регистр допускает как запись, так и чтение. После аппаратного сброса все биты регистра (кроме специально оговоренных исключений) обнулены. Назначение бит регистра команд:

• бит 0 — IO Space— разрешение ответа на обращения к пространству ввода-вывода;

• бит 1 — Memory Space— разрешение ответа на обращения к пространству памяти;

• бит 2 — Bus Master— разрешение работы инициатором (в режиме управления шиной);

• бит 3 — Special Cycles— разрешение реакции на специальные циклы;

• бит 4 — Memory Write and Invalidate enable— разрешение использовать команды «запись с инвалидацией» при работе инициатором (если бит обнулен, то вместо этих команд должна использоваться обычная запись в память);

• бит 5 — VGA palette snoop— разрешение слежения за записью в регистр палитр;

• бит 6 — Parity Error Response— разрешение нормальной реакции (вырабатывать сигнал PERR#) на обнаруженную ошибку паритета (если бит обнулен, то устройство должно только фиксировать ошибку в регистре состояния, в то время как генерация бита паритета устройством выполняется всегда);

• бит 7 — Stepping Control— возможность пошагового переключения (address/data stepping) линий (если устройство никогда этого не делает, бит регистра «запаян» в «0», если делает всегда — в «1», устройство с такой возможностью по сбросу устанавливает этот бит в «1»);

• бит 8 — SERR# Enable— разрешение генерации сигнала ошибки SERR#(ошибка паритета адреса сообщается, когда этот бит и бит 6=1);

• бит 9 — Fast Back-to-Back Enable(необязательный) — разрешение ведущему устройству использовать быстрые смежные обращения к разным устройствам (если бит обнулен, быстрые обращения допустимы лишь для транзакций с одним агентом);

• биты 10–15 — резерв.

♦ Status— регистр состояния, допускающий кроме чтения еще и запись. Однако запись выполняется специфично — с ее помощью можно только обнулять биты, но не устанавливать. Биты, помеченные как RO, допускают только считывание. При записи в позиции обнуляемых бит устанавливаются единичные значения. Назначение бит регистра состояния:

• биты 0–3 — резерв;

• бит 4 — Capability List(RO, необязательный) — указание на наличие указателя новых возможностей (смещение 34h в заголовке);

• бит 5 — 66 MHz Capable(RO, необязательный) — поддержка частоты 66 МГц;

• бит 6 — резерв;

• бит 7 — Fast Back-to-Back Capable(RO, необязательный) — поддержка быстрых смежных транзакций (fast back-to-back) с разными устройствами;

• бит 8 — Master Data Parity Error(только для устройств с прямым управлением) — устанавливается, когда устройство с установленным битом 6 в регистре команд, являясь инициатором, само ввело (при чтении) или обнаружило (при записи) сигнал PERR#;

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)