Естественно, контактные площадки фрагментов должны совпадать с шагом устанавливаемого компонента. Эти фрагменты можно вырезать, например, с неисправных компьютерных плат или подобрать из наборов, продающихся в специализированных магазинах по электронике.

В следующих главах говорится о внутренней программной модели процессора, а также о средствах и способах программирования сигнального процессора. А приведенная и описанная здесь схема поможет на практике начать освоение сигнальных процессоров.

Глава 4. Программно-логическая модель

В этой главе говорится о внутренней программно-логической модели процессора и его системе прерываний.

Прежде чем начать разрабатывать программы для сигнального процессора, необходимо познакомиться с его программно- логической моделью, системой команд и программными инструментами. Освоение данного материала потребует времени и терпения. Но без хорошего знания этих основ невозможно будет научиться программировать сигнальный процессор.

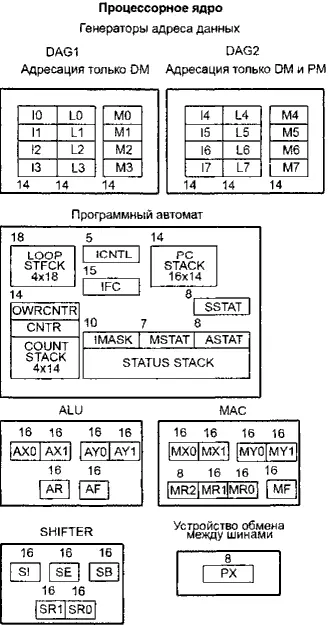

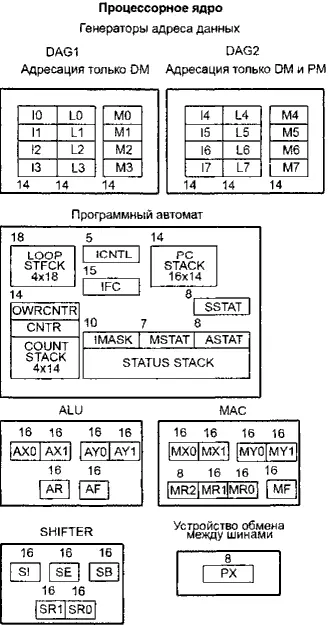

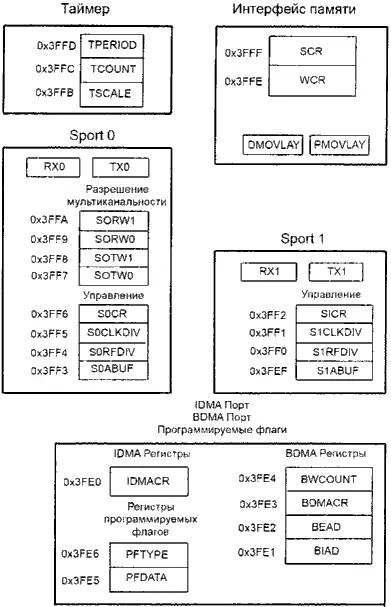

Итак, начнем с программно-логической модели процессора. Такая модель для ADSP-2181 приведена на рис. 4.1.

Рис. 4.1. Программно-логическая модель ADSP-2181

На ней представлены все регистры процессора с указанием их размерности и условными обозначениями. Несмотря на многочисленность этих регистров, все они систематически распределены по логическим блокам процессора, что позволяет понять их назначение без особого труда.

Главный блок регистров представлен на рисунке слева, в процессорном ядре. В первую очередь это блоки регистров программных генераторов адреса DAG1 и DAG2. Данные блоки регистров включают в себя индексные регистры I, регистры длины буфера L и регистры-модификаторы M.

Все перечисленные регистры имеют размерность 14 бит. Эти регистры позволяют организовывать в памяти процессора циклические и линейные буферы, с автоматическим инкрементом адреса слов в этих буферах и отслеживанием их длины. В каждом из блоков генераторов адресов присутствует по четыре группы таких регистров. Использование этих и других регистров будет рассмотрено позже на конкретных примерах.

Блок программного автомата содержит регистры, отвечающие за автоматические операции процессора. В их число входят:

• программный счетчик с 16-уровневым 14-разрядным стеком PC STACK, для организации вызова подпрограмм и обработки прерываний;

• счетчик циклов CNTR с 4-уровневым 14-разрядным стеком COUNT STACK, для организации вложенных программных циклов;

• псевдорегистр OWRCNTR, для обновления значения счетчика CNTR;

• цикловой компаратор LOOP STACK с 4-уровневым 18-разрядным стеком, для обеспечения выполнения программных циклов без тактов ожидания.

Назначение остальных регистров управления и состояния блока программного автомата процессора, приводится в табл. 4.1. Обращение к этим регистрам из программы производится по их логическим именам, совпадающим с именами, приведенными на рис. 4.1 и в табл. 4.1.

Таблица 4.1а Регистр состояния арифметико-логического устройства ASTAT

| Разряд |

Исходное состояние |

Назначение |

| 7 |

0 |

Флаг знака ввода в устройство сдвига SHIFTER (SS) |

| 6 |

0 |

Флаг переполнения в умножителе-накопителе MAC (MV) |

| 5 |

0 |

Флаг частного АЛУ (AQ) |

| 4 |

0 |

Флаг знака ввода порта X в АЛУ (AS) |

| 3 |

0 |

Флаг переноса бита в АЛУ (АС) |

| 2 |

0 |

Флаг переполнения АЛУ (AV) |

| 1 |

0 |

Флаг отрицательного результата в АЛУ (AN) |

| 0 |

0 |

Флаг нулевого значения в АЛУ (AZ) |

Таблица 4.1б Регистр состояния режима процессора MSTAT

| Разряд |

Исходное состояние |

Назначение |

| 6 |

0 |

Разрешение режима GO |

| 5 |

0 |

Разрешение работы таймера |

| 4 |

0 |

Результаты умножителя: 0 — дробные, 1 — целые |

| 3 |

0 |

Разрешение режима насыщения регистра AR АЛУ |

| 2 |

0 |

Разрешение режима фиксации переполнения АЛУ |

| 1 |

0 |

Разрешение бит-реверсивной адресации DAG1 |

| 0 |

0 |

Выбор банка регистров данных: 0 — главный, 1 — теневой |

Таблица 4.1в Регистр разрешения прерываний IMASK (0 — запрещено, 1 — разрешено)

| Разряд |

Исходное состояние |

Назначение |

| 15…10 |

0 |

Не используются |

| 9 |

0 |

-IRQ2 |

| 8 |

0 |

-IRQL1 |

| 7 |

0 |

-IRQL0 |

| 6 |

0 |

Передатчик SPORT0 |

| 5 |

0 |

Приемник SPORT0 |

| 4 |

0 |

-IRQE |

| 3 |

0 |

BDMA |

| 2 |

0 |

Передатчик SPORT1 или -IRQ1 |

| 1 |

0 |

Приемник SPORT0 или -IRQ0 |

| 0 |

0 |

Таймер |

Таблица 4.1г Регистр состояния стека SSTAT

Читать дальше