Выводы порта SPORT1 являются многофункциональными. Они могут быть запрограммированы как на работу с последовательными устройствами подобно порту SPORT0, так и в альтернативном режиме как флаги входа-выхода и входы прерывания. В нашей схеме используется второй способ их применения. Вывод 51 порта будет работать как выход, а вывод 55 как вход. Кроме того, задействован вход прерывания IRQ1, для формирования прерывания процессора при поступлении информации по сигнальному выводу FI. Эти выводы задействованы для организации последовательного порта RS-232 или проще — компьютерного СОМ порта. Для этого они подключены к микросхеме преобразования уровней DA2. Эта микросхема преобразует ТТЛ уровни сигнала в уровни стандарта RS-232. Конденсаторы C12–C15 обеспечивают работу внутренних умножителей напряжения в микросхеме. Сигналы порта RS-232 выведены на девятиштырьковый разъем XRS1. Назначение сигналов на этом разъеме соответствует стандарту, принятому для персональных компьютеров IBM PC. В дальнейшем к этому порту можно подключить компьютер, с помощью нуль-модемного кабеля, для загрузки обучающих программ с помощью программного пакета EZ-KIT Lite, распространяемого фирмой Analog Device.

Сигналы А0–А13 являются адресными и предназначены для адресации внешней памяти или устройств ввода-вывода. В схеме они подключены к адресным выводам микросхемы постоянной памяти D7, а некоторые из них, к дешифратору устройств ввода-вывода D9.

Сигналы D0–D23 предназначены для передачи данных и для адресации. Младшие восемь бит этой шины участвуют в обмене данными только с расширенной памятью. В нашей схеме эта память не подключена и, соответственно, сигналы D0–D7 не задействованы. Разряды D8–D15 используются для передачи данных при обращении к байтовой памяти BDMA.

В нашей схеме эту роль выполняет микросхема постоянной флэш-памяти D7. Наконец, старшие разряды этой шины D16–D23 выполняют двоякую роль. При обращении к байтовой памяти они несут функцию старших адресных линий, а при обращении к устройствам ввода-вывода являются старшими разрядами шины данных.

Далее следуют сигналы записи -WR, чтения -RD и выборки внешних устройств. В нашей схеме из внешних устройств будет использоваться байтовая память D7, выбираемая сигналом -BMS с помощью дешифратора D8, и устройства ввода-вывода, выбираемые сигналом -IOMS с помощью дешифратора D9 и логических элементов D13.1, D13.2. В схеме присутствует восьмиразрядный регистр ввода D11 и восьмиразрядный регистр вывода D12. Первый из них позволяет снимать дискретные сигналы с различных цифровых датчиков, контактов и пр. А второй обеспечивает возможность управления цифровыми ключами, индикаторами и т.п. Выводы этих регистров заведены на разъемы XI и ХО соответственно.

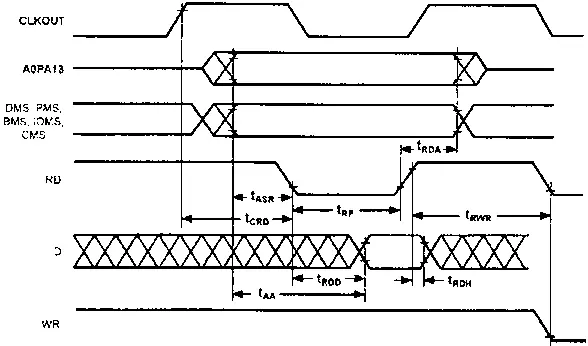

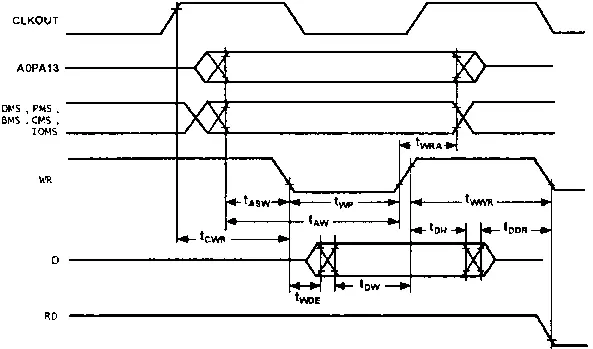

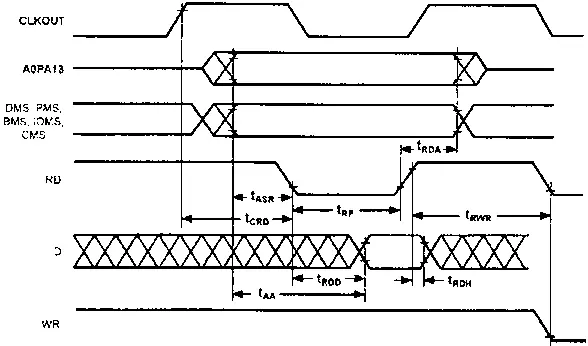

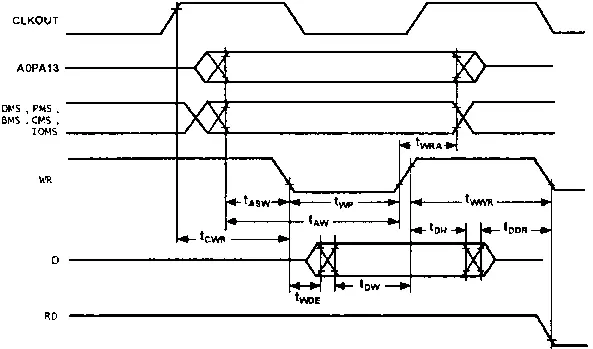

Временные диаграммы циклов чтения и записи данных процессором, представлены на рис. 3.3 и 3.4, соответственно. Параметры сигналов для этих циклов приводятся в табл. 3.4 и 3.5.

Рис. 3.3. Временная диаграмма цикла чтения

Рис. 3.4. Временная диаграмма цикла записи

Таблица 3.4 Параметры сигналов для цикла чтения данных процессором

| Параметр |

Минимум |

Максимум |

Единица измерения |

| Чтение памяти |

| Требуемые длительности: |

| t RDD |

|

0,5 t CK- 9 + w |

нс |

| t AA |

|

0,25 t CK- 10.5 + w |

нс |

| t RDH |

0 |

|

нс |

| Характеристика переключения: |

| t RP |

0,5 t CK- 5 + w |

0,25 t CK+ 7 |

нс |

| t CRD |

0,25 t CK- 5 |

|

нс |

| t ASR |

0,25 t CK- 6 |

|

нс |

| t RDA |

0,25 t СK- 3 |

|

нс |

| t RWR |

0,5 t CK- 5 |

|

нс |

Таблица 3.5 Параметры сигналов для цикла записи данных процессором

| Параметр |

Минимум |

Максимум |

Единица измерения |

| Запись памяти |

| Характеристика переключения: |

| t DW |

0,5 t СK- 7 + w |

|

нс |

| t DH |

0,25 t СK- 2 |

|

нс |

| t WP |

0,5 t CK- 5 + w |

|

нс |

| t WDE |

0 |

|

нс |

| t ASW |

0,25 t CK- 6 |

|

нс |

| t DDR |

0,25 t CK- 7 |

|

нс |

| t CWR |

0,25 t CK- 5 |

|

нс |

| t AW |

0,75 t CK- 9 + w |

0,25 t СK+ 7 |

нс |

| t WRA |

0,25 t CK- 3 |

|

нс |

| t WWR |

0,5 t CK- 5 |

|

нс |

* w — число циклов задержки * t CK

Из приведенных данных видно, что чтение и запись данных в процессор необходимо производить по нарастающему фронту сигналов чтения или записи соответственно, когда обеспечена достоверность данных на шине.

Читать дальше