– Элемент 9 выполняет операцию И-НЕ: сначала умножает поступающие на его входы сигналы 0 и 0, а затем полученный результат инвертирует. В результате на выходе элемента формируется сигнал 1, который далее проходит ( розовая стрелка) на вход элемента 10.

д) В конце срабатывает элемент 10, который выполняет операцию ИЛИ-НЕ: сначала делает логическое сложение поступающих на его входы сигналов 0 и 1, а затем полученный результат инвертирует. В результате на выходе элемента формируется сигнал 0, который проходит на выход схемы Y.

3. Анализ работы схемы в динамическом режиме.

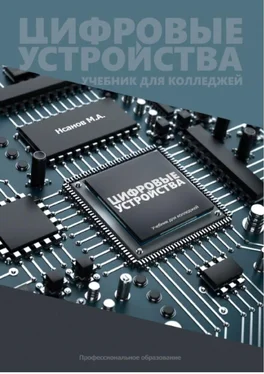

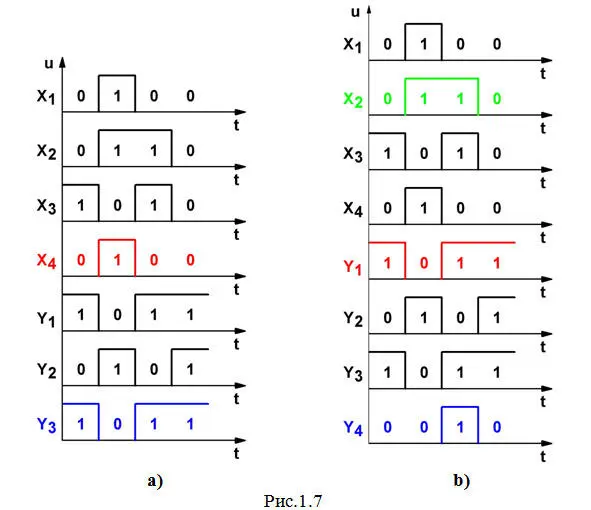

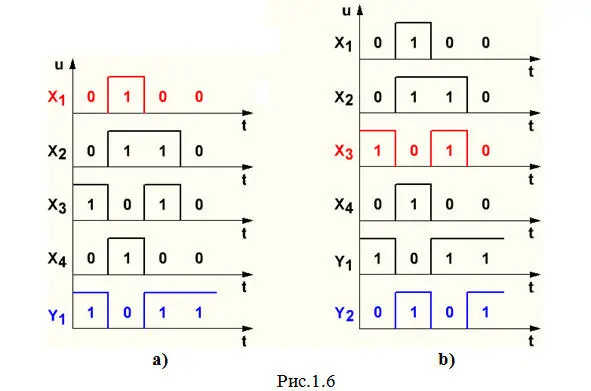

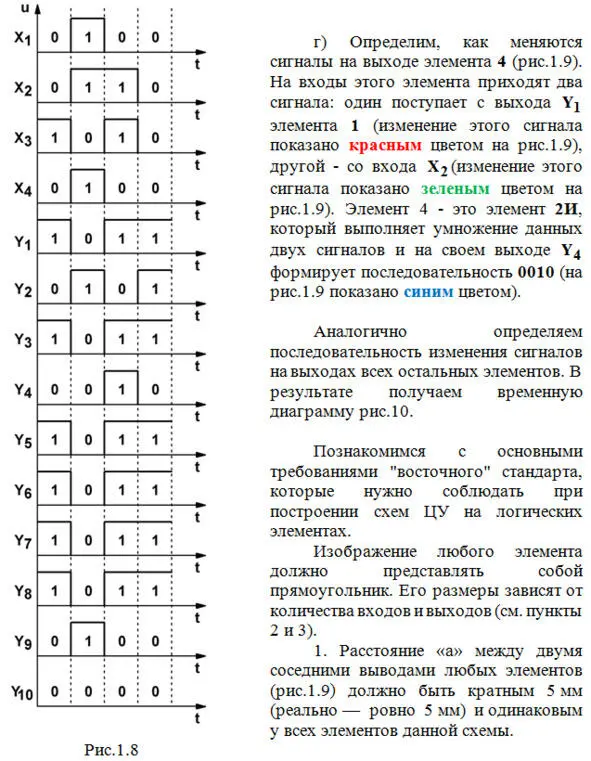

а) Сначала определим, как меняются сигналы на выходе элемента 1 (рис.1.6а). На вход этого элемента сигналы поступают со входа X 1(показано краснымцветом на рис.1.6а), которые меняются следующим образом: в первом такте – 0, во втором – 1, в третьем – 0, в четвертом – 0. Элемент 1 – это элемент НЕ, который инвертирует данные поступающие сигналы и на своем выходе Y 1формирует последовательность 1011 (на рис.1.6а показано синимцветом).

б) Теперь рассмотрим изменение сигналов на выходе элемента 2 (рис.1.6b). На оба входа этого элемента поступают сигналы со входа X 3(показано краснымцветом на рис.1.6b), которые меняются так: в первом такте – 11, во втором – 00, в третьем – 11, в четвертом – 00. Элемент 2 – это элемент 2И-НЕ, который выполняет умножение данных поступающих сигналов с последующим инвертированием полученных результатов и на своем выходе Y 2формирует последовательность 0101 (на рис.1.6b показано синимцветом).

По полученным результатам можно сделать еще один важный вывод: элементы И-НЕ (а также элементы ИЛИ-НЕ) с объединенными входами выполняют функцию элемента НЕ, т.е. производят инвертирование поступающих сигналов .

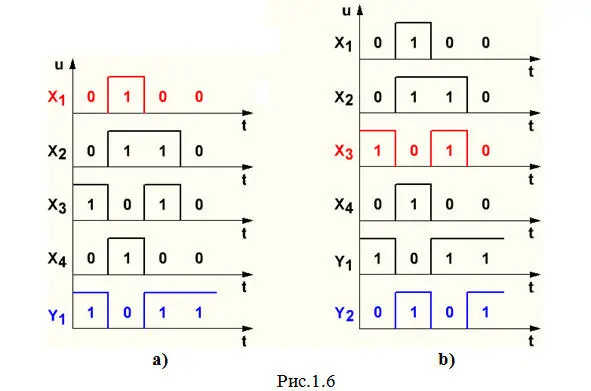

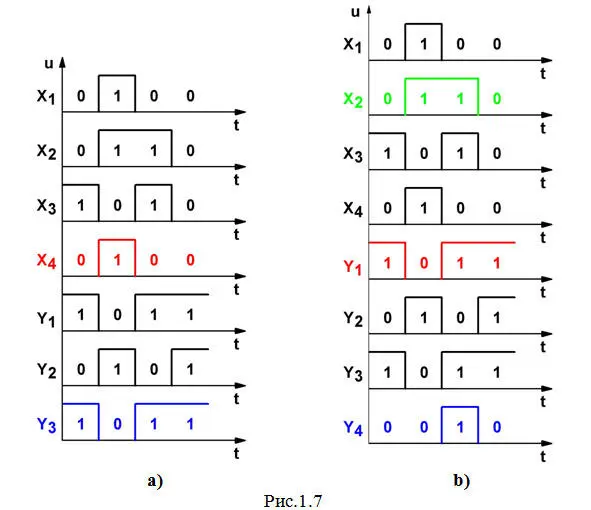

в) Далее проанализируем изменение сигналов на выходе элемента 3 (рис.1.7a). На вход этого элемента сигналы поступают со входа X 4(показано краснымцветом на рис.1.7a), которые меняются следующим образом: в первом такте – 0, во втором – 1, в третьем – 0, в четвертом – 0. Элемент 3 – это элемент НЕ, который инвертирует данные поступающие сигналы и на своем выходе Y 3формирует последовательность 1011 (на рис.1.7a показано синимцветом).

1.3. Интегральные микросхемы (ИМС). Маркировка ИМС

Логические элементы выпускаются в виде интегральных микросхем (ИМС или просто ИС). ИМС называют схему, компоненты которой нераздельно связаны и электрически соединены между собой так, что все устройство рассматривается как единое целое. Функциональную сложность любой ИМС принято характеризовать степенью интеграции – количеством компонентов Nв микросхеме. По степени интеграции различают:

– ИМС малой степени интеграции: менее 100;

– ИМС средней степени интеграции: N = 100 ÷ 1000;

– БИС (большие интегральные схемы): N = 1000 ÷ 10000;

– СБИС (сверхБИС): N = 10000 ÷ 10 6 (миллион);

– УБИС (ультраБИС): N = 10 6 ÷ 10 9 (миллиард);

– ГБИС (гигаБИС): более 10 9.

В данной книге рассматриваются в основном элементы цифровой техники и ЦУ, выпускаемые преимущественно в виде ИМС средней степени интеграции и БИС.

Внимание! Следует всегда иметь в виду, что элементы цифровой техники и различные цифровые устройства выпускаются как в виде отдельных микросхем средней степени интеграции и БИС, так и входят составными частями в микросхемы БИС, СБИС, УБИС и ГБИС многофункциональных ЦУ. Например: в АЛУ, интерфейсы, микропроцессоры и другие специализированные микросхемы отдельных отраслей техники, которые изучаются как в данном предмете, так и в соответствующих специальных курсах. Но в любом случае принцип их работы, структура и назначение выводов остаются одинаковыми!

Читать дальше