Сегмент sync_segиспользуется, чтобы синхронизировать узлы CAN сети. Сегмент имеет длину, равную одному кванту времени. В течение этого периода контроллер msCAN12 ожидает фронт сигнала. Длительность time segment 1может составлять от 4 до 16 квантов времени, что определяется состоянием битов 0…3 регистра синхронизации шины CBTR1 (рис. 9.26). Длительность этого сегмента должна программироваться в соответствии с задержкой распространения передатчика и приемника, а также фазовой ошибкой фронта сигнала. Продолжительность сегмента time segment 2составляет от 2 до 8 квантов времени, и может также программироваться, с помощью битов 4, 5 и 6 регистра CBTR1. Таким образом, продолжительность времени передачи одного бита может составлять от 7 до 25 квантов времени в зависимости от установки битов в регистре CBTR1.

Рис. 9.26.Формат регистра CBTR1

Биты от 0 до 3 (TSEG13, TSEG12, TSEG11, и TSEG10) используются, чтобы установить длительность time segment 1, в соответствии с табл. 9.2. Биты от 4 до 6 (TSEG22, TSEG21 и TSEG20) используются, чтобы конфигурировать время time segment 2, как показано в табл. 9.3. Бит SAMP определяет, будет ли использоваться одна или три выборки, чтобы измерить принимаемый бит сообщения. Если бит SAMP установлен, используются три выборки, если он очищен, то только одна. Регистр CBTR1 может изменяться только при установленном бите SFTRES в регистре CMCR0.

| TSEG13 |

TSEG12 |

TSEG11 |

TSEG10 |

time segment 1 |

| 0 |

0 |

0 |

0 |

1 квант времени |

| 0 |

0 |

0 |

1 |

2 кванта времени |

| 0 |

0 |

1 |

0 |

3 кванта времени |

| 0 |

0 |

1 |

1 |

4 кванта времени |

| … |

… |

… |

… |

… |

| 1 |

1 |

1 |

1 |

16 квантов времени |

Таблица 9.2.Конфигурация длительности time segment 1

| TSEG22 |

TSEG21 |

TSEG20 |

time segment 2 |

| 0 |

0 |

0 |

1 квант времени |

| 0 |

0 |

1 |

2 кванта времени |

| 0 |

1 |

0 |

3 кванта времени |

| 0 |

1 |

1 |

4 кванта времени |

| … |

… |

… |

… |

| 1 |

1 |

1 |

8 квантов времени |

Таблица 9.3.Конфигурация длительности time segment 2

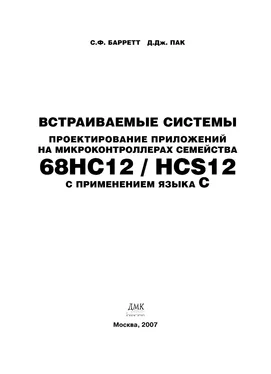

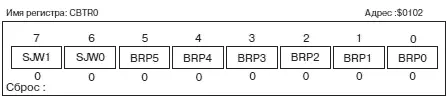

Вернемся теперь к битам 7 и 6 регистра CBTR0. При синхронизации битов на шине, используются биты скачка ресинхронизации (SJW1:SJW0), позволяющие уменьшить или увеличить ширину скачка ресинхронизации (число квантов времени). Таблица 9.4 показывает ширину скачка ресинхронизации, соответствующую различным значениям SJW1:SJW0.

| SJW1 |

SJW0 |

Ширина скачка ресинхронизации |

| 0 |

0 |

1 квант времени |

| 0 |

1 |

2 кванта времени |

| 1 |

0 |

3 кванта времени |

| 1 |

1 |

4 кванта времени |

Таблица 9.4.Выбор ширины скачка ресинхронизации

В заключение покажем дополнительную аппаратную возможность контроллера msCAN12 контроллера. Когда контроллер принял или передал корректное сообщение, генерируется импульс с длительностью, равной времени передачи одного бита. Этот импульс может быть послан на встроенный модуль таймерного интерфейса (TIM). Чтобы установить эту внутреннюю связь, используется бит TLNKEN в регистре CMCR0. Такое решение обеспечивает программисту необходимую гибкость. Модуль таймерного интерфейса может быть запрограммирован на определенное действие при появлении любого кадра приема или передачи, например, для каждого кадра может создаваться своя собственная метка времени.

9.3.4. Конфигурирование модуля msCAN12 для работы в сети

В этом разделе мы объединим три подсистемы контроллера msCAN12 в единое целое и покажем последовательность действий по его инициализации.

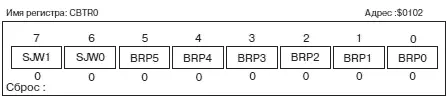

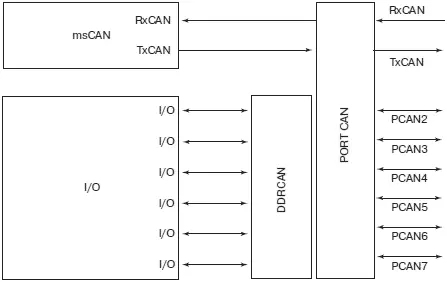

До начала нашего обсуждения конфигурации сети, отметим, что шесть из восьми выводов физического порта CAN могут использоваться как универсальные входы/выходы порта общего назначения PORTCAN. На рис. 9.27 показано использование порта CAN для таких целей. Когда выводы со 2 по 7 находятся в режиме универсальных линий ввода/вывода, следующие три регистра используются для записи и чтения данных с порта PORTCAN: регистр данных PORTCAN, регистр направления передачи DDRCAN, регистр управления PCTLCAN.

Рис. 9.27.CAN портовая конфигурация

Регистр DDRCAN используется, чтобы программировать соответствующие выводы как входные или выходные. На рис. 9.28 показано назначение каждого бита регистра. Обратите внимание, что биты 0 и 1 зарезервированы как биты передачи и приема контроллера CAN и не могут быть использованы как универсальные выводы входов/выходов. Установка бита направления передачи данных в состояние логической 1 конфигурирует соответствующий вывод как выходной; установка его в состояние логического нуля — как входной. Регистр PCTLCAN, формат которого представлен на рис. 9.29, используется, чтобы разрешать или запрещать перевод выводов от 2 до 7 порта CAN в режим драйверов высокого или низкого уровня. Бит PUECAN используется, разрешать (при переводе в состояние логической 1) или запрещать (при переводе в состояние логического 0) режим драйвера высокого уровня. Бит RDPCAN выбирает конфигурацию, разрешающую (при переводе в состояние логической 1) или запрещающую (при переводе в состояние логического 0) режим драйвера низкого уровня.

Читать дальше