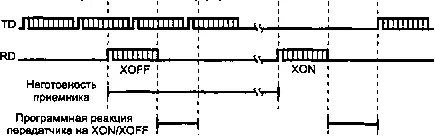

Программный протокол управления потоком XON/XOFF предполагает наличие двунаправленного канала передачи данных. Работает протокол следующим образом: если устройство, принимающее данные, обнаруживает причины, по которым оно не может их дальше принимать, оно по обратному последовательному каналу посылает байт-символ XOFF(13h). Противоположное устройство, приняв этот символ, приостанавливает передачу. Когда принимающее устройство снова становится готовым к приему данных, оно посылает символ XON(11h), приняв который противоположное устройство возобновляет передачу. Время реакции передатчика на изменение состояния приемника по сравнению с аппаратным протоколом увеличивается, по крайней мере, на время передачи символа ( XONили XOFF) плюс время реакции программы передатчика на прием символа (рис. 2.14). Из этого следует, что данные без потерь могут приниматься только приемником, имеющим дополнительный буфер принимаемых данных и сигнализирующим о неготовности заблаговременно (имея в буфере свободное место).

Рис. 2.14. Программное управление потоком XON/XOFF

Преимущество программного протокола заключается в отсутствии необходимости передачи управляющих сигналов интерфейса — минимальный кабель для двустороннего обмена может иметь только 3 провода (см. рис. 2.5, а ). Недостатком, помимо обязательного наличия буфера и большего времени реакции (снижающего общую производительность канала из-за ожидания сигнала XON), является сложность реализации полнодуплексного режима обмена. В этом случае из потока принимаемых данных должны выделяться (и обрабатываться) символы управления потоком, что ограничивает набор передаваемых символов.

Кроме этих двух распространенных стандартных протоколов, поддерживаемых и ПУ, и ОС, существуют и другие.

2.5. Микросхемы асинхронных приемопередатчиков

В СОМ-портах преобразование параллельного кода в последовательный для передачи и обратное преобразование при приеме данных выполняют специализированные микросхемы UART (Universal Asynchronous Receiver-Transmitter — универсальный асинхронный приемопередатчик). Эти же микросхемы формируют и обрабатывают управляющие сигналы интерфейса. СОМ-порты IBM PC XT/AT базируются на микросхемах, совместимых на уровне регистров с UART i8250 — 8250/16450/16550А. Это семейство представляет собой усовершенствование начальной модели, направленное на повышение быстродействия, снижение потребляемой мощности и загрузки процессора при интенсивном обмене. Отметим, что:

♦ 8250 имеет ошибки (появление ложных прерываний), учтенные в XT BIOS;

♦ 8250А — ошибки исправлены, но в результате потеряна совместимость с BIOS; эта микросхема работает в некоторых моделях AT, но непригодна для скорости 9600 бит/с;

♦ 8250В — исправлены ошибки 8250 и 8250A, восстановлена ошибка в прерываниях — возвращена совместимость с XT BIOS; работает в AT под DOS (кроме скорости 9600 бит/с).

Микросхемы 8250x имеют невысокое быстродействие по обращениям со стороны системной шины. Они не допускают обращения к своим регистрам в смежных шинных циклах процессора — для корректной работы с ними требуется введение программных задержек между обращениями CPU. В компьютерах класса AT применяют микросхемы UART перечисленных ниже модификаций.

♦ 16450 — быстродействующая версия 8250 для AT. Ошибок 8250 и полной совместимости с XT BIOS не имеет.

♦ 16550 — развитие 16450. Может использовать канал DMA для обмена данными. Имеет FIFO-буфер, но некорректность его работы не позволяет им воспользоваться.

♦ 16550А — имеет работающие 16-байтные FIFO-буферы приема и передачи и возможность использования DMA. Именно этот тип UART должен применяться в AT при интенсивных обменах на скоростях 9600 бит/с и выше. Совместимость с этой микросхемой обеспечивает большинство микросхем контроллеров портов ввода-вывода, входящих в современные чипсеты.

Микросхемы UART 16550А с программной точки зрения представляют собой набор регистров, доступ к которым определяется адресом (смещением адреса регистра относительно базового адреса порта) и значением бита DLAB(бита 7 регистра LCR). В адресном пространстве микросхема занимает 8 смежных адресов. Список регистров UART 16550A и способы доступа к ним приведены в табл. 2.4. Микросхемы 8250 отличаются отсутствием регистра FCR и всех возможностей FIFO и DMA.

Таблица 2.4. Регистры UART 16550A

Читать дальше

![Михаил Барятинский - Танки III Рейха. Том II [Самая полная энциклопедия]](/books/427750/mihail-baryatinskij-tanki-iii-rejha-tom-ii-samaya-thumb.webp)

![Михаил Барятинский - Танки III Рейха. Том I [Самая полная энциклопедия]](/books/427751/mihail-baryatinskij-tanki-iii-rejha-tom-i-samaya-p-thumb.webp)