1Начало записи: -IS=0 и -IWR=0.

2Конец записи: -IS=1 или -IWR=1.

Во время длинного цикла данные читаются и записываются с ожиданием готовности порта по сигналу -IACK, который активизируется только после непосредственной записи или чтения данных в памяти процессора.

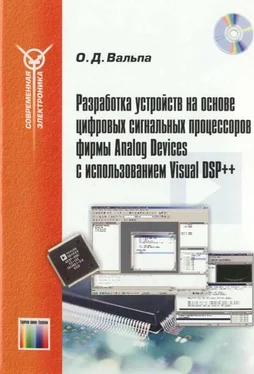

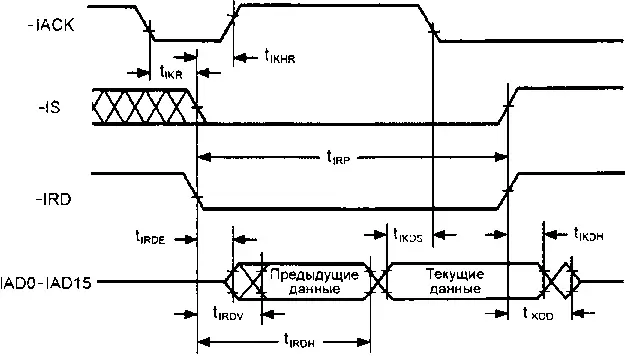

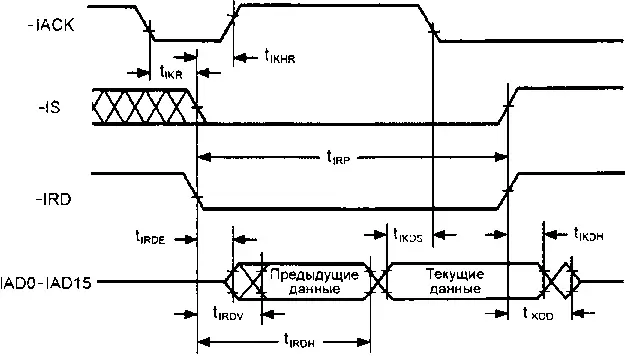

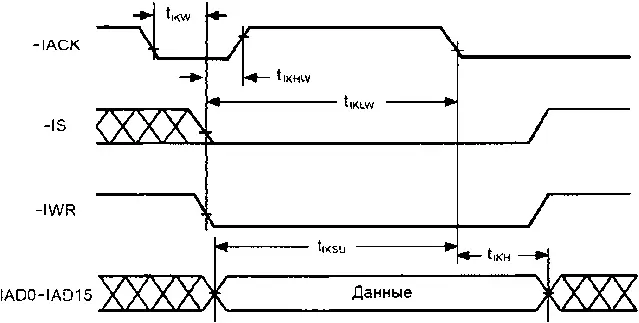

Временные диаграммы для данных циклов обращения показаны на рис. 8.5 и 8.6 соответственно. В табл. 8.5 и 8.6 приведены характеристики сигналов для этих диаграмм.

Рис. 8.5. Временные диаграммы длинного цикла чтения через порт IDMA

Рис. 8.6. Временные диаграммы длинного цикла записи через порт IDMA

Таблица 8.5 Временные параметры диаграммы длинного цикла чтения через порт IDMA

| Параметр |

Минимум |

Максимум |

| Длинный цикл чтения через IDMA |

| Требуемые длительности: |

| t IKR-IACK=0 до начала чтения 1, нс |

0 |

|

| t IRPПродолжительность сигнала чтения, нс |

15 |

|

| Характеристики переключения: |

| t IKHR-IACK=0 после начала чтения 1, нс |

|

15 |

| t IKDSУстановка данных перед -IACK=0, нс |

0,5 t CK 5-10 |

|

| t IKDHУдержание данных после окончания чтения 2, нс |

0 |

|

| t IKDDСброс данных после окончания чтения 2, нс |

|

10 |

| t IRDEАктивизация предыдущих данных, нс |

0 |

|

| t IRDVДостоверность предыдущих данных, нс |

|

15 |

| t IRDH1Удержание предыдущих данных (DM/PM1), нс |

2 t CK-5 |

|

| t IRDH2Удержание предыдущих данных (PM2), нс |

t CK-5 |

|

Примечания:

1Начало чтения: -IS=0 и -IRD=0.

2Конец чтения:-IS=1 или -IRD=1.

3Чтение памяти DM или первой половины РМ.

4Чтение второй половины РМ.

5t CK— период тактовой частоты процессора.

Таблица 8.6 Временные параметры диаграммы длинного цикла записи через порт IDMA

| Параметр |

Минимум |

Максимум |

| Длинный цикл записи через IDMA |

| Требуемые длительности: |

| t IKW-IACK=0 до начала записи 1, нс |

0 |

|

| t IKSUУстановка данных перед -IACK=0, нс |

0,5 t CK 2+1 |

|

| t IKHУдержание данных после -IACK=0, нс |

2 |

|

| Характеристики переключения: |

| t IKLWОт начала записи до -IACK=0, нс |

1,5 t CK |

|

| t IKHWОт начала записи до -IACK=1, нс |

|

15 |

Примечания:

1Начало записи: -IS=0 и -IWR=0.

2t СK— период тактовой частоты процессора.

Сигнал подтверждения данных -IACK допускается не использовать, если скорость обращения к порту со стороны адаптера невысокая и достоверность данных обеспечивается задержкой самих сигналов управления.

При обращении через порт IDMA к памяти данных операции чтения и записи выполняются за один цикл, поскольку разрядность порта составляет 16 бит. Однако при обращении к 24-разрядным данным памяти программ требуется два цикла обращения. В первом цикле происходит чтение или запись старших 16 бит слова памяти программ. Во втором цикле по линиям IAD0–IAD7 передаются младшие 8 бит слова. Линии IAD8–IAD15 при этом игнорируются. Автоинкремента адреса между этими циклами не происходит.

Через порт IDMA возможен доступ ко всей памяти процессора, за исключением регистров управления и состояния, отображенных на область памяти данных. При обращении через IDMA к области памяти данных, отведенной для регистров управления и состояния с адреса 0x3FE0 по адрес 0x3FFF, запись и чтение данных все же будет производиться. Но эта область памяти фактически будет дополнительной для пользователя, поскольку она дублирует системную область памяти данных, отведенную для регистров управления и состояния процессора.

Данную область допускается использовать для хранения произвольной служебной информации, но только при обращении к этой памяти через порт IDMA, поскольку другой возможности обращения к данной памяти у процессора не существует. Для обеспечения доступа через порт IDMA к регистрам управления и состояния процессора необходимо обеспечить пересылку содержимого этих регистров в другую область памяти из самой программы процессора. Такая аппаратная конфигурация процессора обеспечивает защиту информации в регистрах управления и состояния от случайной записи и от программных ошибок.

Процессор ADSP-2181 поддерживает также начальную загрузку программ в память программ через порт IDMA. Для этого необходимо установить сигналы на выводах процессора BMODE=1 и MMAP=0. Затем необходимо произвести сброс процессора и загрузить программу в память программ процессора, начиная с адреса 1 через порт IDMA. Кроме того, можно записать произвольные данные в память данных процессора. После этого следует записать слово программы по адресу 0, и процессор запустит загруженную программу.

Читать дальше