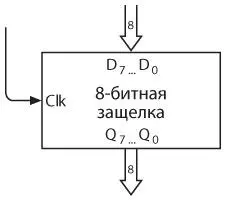

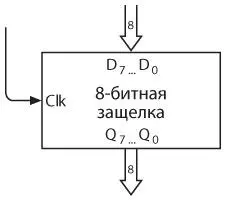

Эта защелка способна одновременно хранить восемь бит информации. Восемь входов сверху обозначены от D0 до D7, а восемь выходов внизу — от Q0 до Q7. Слева расположен вход «Синхронизация» (Clk). Сигнал Clk обычно равен 0. Когда сигнал Clk — 1, то 8-битное значение на входах D передается на выходы Q. Когда сигнал Clk возвращается к 0, тогда 8-битное значение сохраняется там, пока сигнал Clk снова не станет равен 1.

Восьмибитную защелку также можно изобразить с восемью входами «Данные» и восемью выходами Q, сгруппированными вместе.

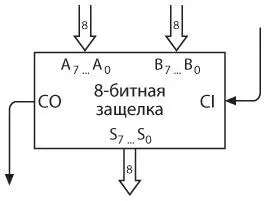

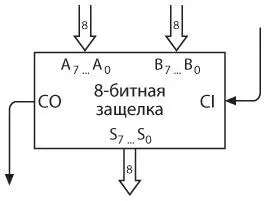

Вот схема 8-битного сумматора.

Обычно (если проигнорировать то, что мы делали с вычитанием в предыдущей главе), восемь входов A и восемь входов B подключены к переключателям, вход для переноса CI — к земле, а восемь выходов S и CO — к лампочкам.

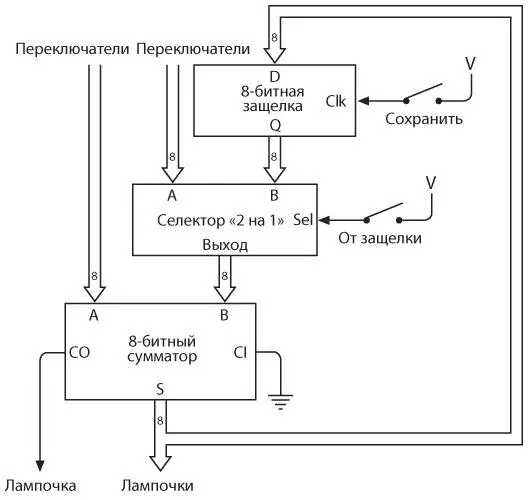

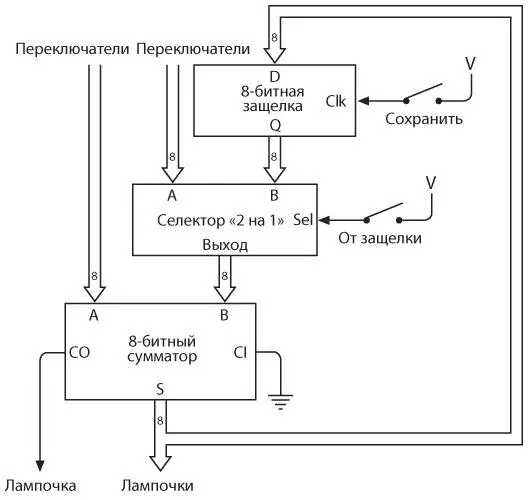

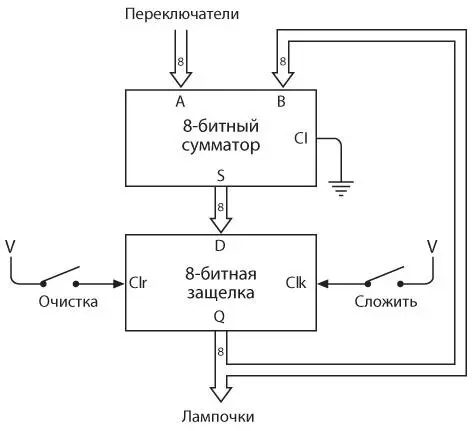

В этой пересмотренной версии восемь выходов S 8-разрядного сумматора могут быть подключены как к лампочкам, так и ко входам D 8-битной защелки. Для сохранения результата работы сумматора можно подключить переключатель «Сохранить» ко входу Clk защелки.

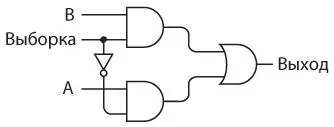

Селектор двух линий на одну позволяет выбрать с помощью переключателя, откуда должны поступать данные на входы B: из второго ряда переключателей или из выходов Q защелки. Замыкание переключателя означает выбор выходов 8-битной защелки. В селекторе «2 на 1» используется восемь следующих схем.

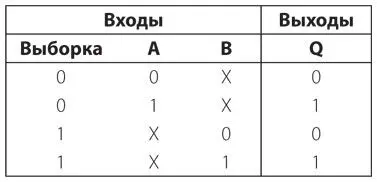

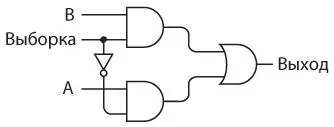

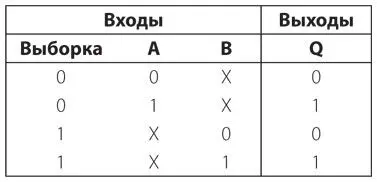

Если вход «Выборка» (или Sel — сокращение от английского Select) равен 1, то значение сигнала на выходе вентиля ИЛИ равно значению сигнала на входе B. Это связано с тем, что выход верхнего вентиля И равен входу B, а выход нижнего вентиля И — 0. Если вход «Выборка» равен 0, выход будет совпадать со входом A. Эти правила представлены в следующей функциональной таблице.

Селектор, являющийся частью модифицированного сумматора, включает восемь таких однобитных селекторов. Все входы «Выборка» соединены между собой.

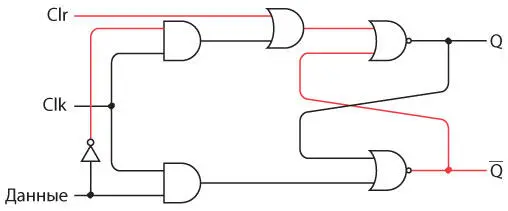

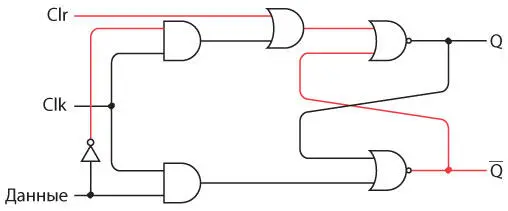

Этот модифицированный сумматор не вполне корректно обрабатывает сигнал CO (выход для переноса). Если при сложении двух чисел этот сигнал CO становится равным 1, то этот сигнал игнорируется при добавлении к сумме следующего числа. Одно из возможных решений заключается в том, чтобы создать сумматор, защелку и селектор, разрядность которых составляет 16 бит или, по крайней мере, превышает разрядность наибольшей суммы, которая может получиться. Мы не будем приступать к решению этой задачи вплоть до главы 17. Более интересный подход к созданию сумматора позволяет обойтись без ряда из восьми переключателей. Однако сначала нужно немного изменить триггер типа D, добавив вентиль ИЛИ и входной сигнал «Очистка» (Clear, или Clr). Вход Clr обычно равен 0. Когда он равен 1, выход Q — 0.

Сигнал Q становится равным 0 вне зависимости от других входных сигналов, что приводит к стиранию информации, сохраненной в триггере.

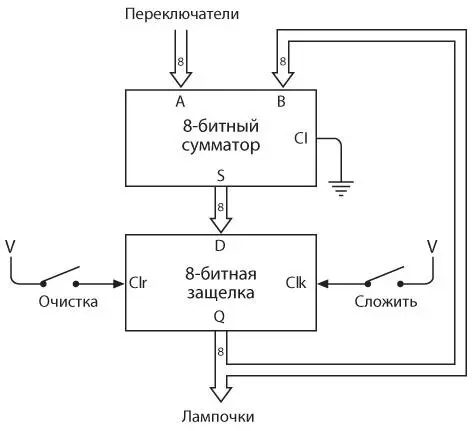

Вы можете спросить: зачем это нужно? Почему мы не можем очистить триггер, подав на вход «Данные» 0, а на вход Clk — 1? Может быть, мы не можем точно контролировать то, что подается на вход «Данные»? Возможно, у нас есть набор из восьми таких защелок, подключенных к выходам 8-битного сумматора, как показано ниже.

Обратите внимание: переключатель с меткой «Сложить» теперь управляет входом защелки Clk.

Может показаться, что этот сумматор использовать проще, чем предыдущий, особенно если требуется сложить множество чисел. Сначала вы нажимаете кнопку «Очистка». В результате выходы защелок становятся равными 0, все лампочки отключаются, а на второй набор входов 8-битного сумматора подаются значения 0. Вы вводите первое число и нажимаете кнопку «Сложить». Это число отображается в виде комбинации горящих лампочек. Затем вводите второе число и снова нажимаете кнопку «Сложить». Число, введенное с помощью переключателей, добавляется к предыдущей сумме, и результат снова отображается с помощью лампочек. Вы можете продолжать вводить новые числа и нажимать кнопку «Сложить». Я уже говорил, что сконструированный нами D-триггер срабатывает по уровню , то есть уровень сигнала на входе Clk должен измениться с 0 на 1, чтобы в защелке сохранилось значение на входе «Данные». Пока сигнал на входе Clk равен 1, значение входа «Данные» может меняться; любые изменения входа «Данные», пока сигнал Clk равен 1, будут отражаться в значениях выходов Q и .

Читать дальше

Конец ознакомительного отрывка

Купить книгу