К моменту прихода 8-го импульса на двух входах J 4-го триггера формируется уровень лог. «1». 8-ым импульсом этот триггер переключается в состояние лог. «1», а уровень лог. «0» с его инверсного выхода, подаваемый на вход «J» второго триггера, запрещает его переключение в единичное состояние под действием 10-го импульса.

10-ый импульс восстанавливает нулевое состояние 4-го триггера и цикл работы счётчика повторяется.

5.3.6 Универсальные счётчики в интегральном исполнении (Примеры)

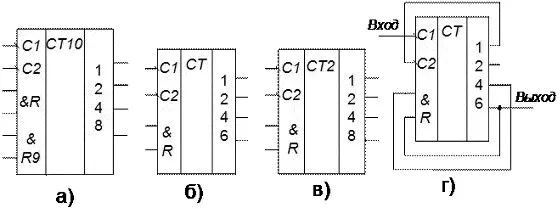

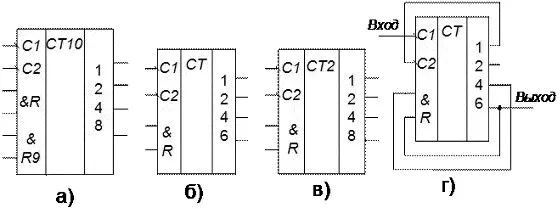

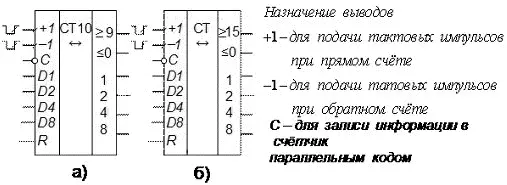

Микросхемы счётчиков К155ИЕ2, К155ИЕ4 и К155ИЕ5,

УГО которых приведены на рисунке 64 а, б, в представляют собой счётчики с последовательно-параллельным переносом, структурные схемы которых подобны схеме, приведённой на рисунке 63.

Рисунок 64 Микросхемы счётчиков К155ИЕ2, К155ИЕ4 и К155ИЕ5

Структурные схемы счётчиков содержат по 4-е JK-триггера в счётном режиме. Первый триггер имеет отдельный вход C1 и прямой выход — 1, три оставшиеся триггера соединены между собой так, что образуют параллельные счётчики с коэффициентами счёта равными 5 (К15ИЕ2), 6 (К155ИЕ4) и 8 (К1ИЕ5).

При соединении выхода первого триггера со входом C2 цепочки из 3-х триггеров образуются счётчики с коэффициентами счёта 10, 12 и 16 соответственно.

Микросхемы имеют по два входа R, объединённые по «И». Микросхема К155ИЕ2 имеет кроме того входы установки в состояние 9, при котором первый и последний разряды устанавливаются в «1», а остальные в «0», то есть 1001 2=9.

Наличие входов установки, например, в «0», позволяет строить делители частоты (счётчики) с различными коэффициентами деления (счёта) в пределах 2–16 без использования дополнительных логических элементов.

На рисунке 61,г показано преобразование счётчика, имеющего K СЧ =12, в десятичный.

До прихода 10-го импульса схема работает как делитель частоты на 12. Десятый импульс переводит триггеры МС в состояние, при котором на выходах 4 и 6 МС формируются лог. «1».

Эти уровни, поступая на входы R, объединённые по «И», переводят МС в состояние «0»; в результате чего K СЧ ( K ДЕЛ ) становится равным 10.

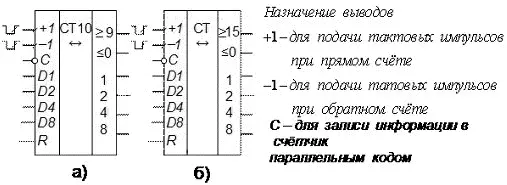

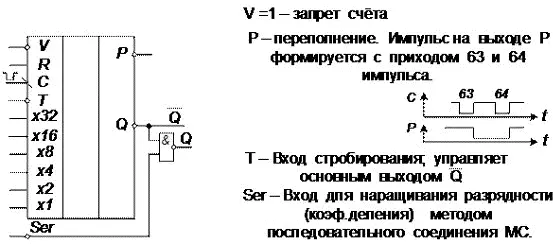

Реверсивные счётчики К155ИЕ6 и К155ИЕ7 (Рисунок 65)

Прямой счёт осуществляется при подаче отрицательных импульсов на вход +1, при этом на входах –1 и C должна быть лог. «1», а на входе R — лог. «0». Переключение триггеров происходит по спадам входных импульсов.

Рисунок 65 Реверсивные счётчики К155ИЕ6 а) и К15ИЕ7 б).

Уровни на выходах 1–2–4–8 соответствуют состоянию счёта в данный момент времени.

Отрицательный импульс на выходе ≥9 (≥15) формируется одновременно с 10 (или 16) импульсом на входе +1. Этот импульс может подаваться на вход +1 следующей МС многоразрядного счётчика. При обратном счёте входные импульсы подаются на вход –1, выходные импульсы снимаются с выхода ≤0.

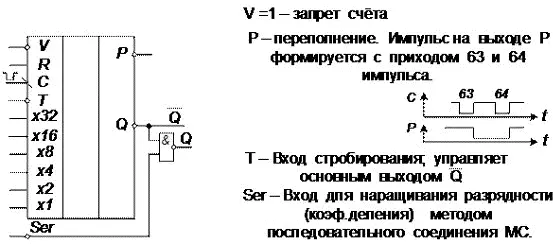

Счётчик-делитель частоты с переменным коэффициентом деления К155ИЕ8 (Рисунок 66).

Микросхема содержит 6-разрядный двоичный счётчик, элементы совпадения и элемент собирания. Элементы совпадения блокируют прохождение импульсов, не совпадающих с запрограммированным кодом, а элемент собирания позволяет передавать на выход только выделенные импульсы.

Рисунок 66 Счётчик – делитель частоты К155ИЕ8

В результате средняя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов.

Число импульсов на выходе  за период счёта (до 64) подсчитывается по формуле: N=32·x32+16·x16+8·x8+4·x4+2·x2+1·x1, где x1–x32 принимают значения соответственно 0 или 1 в зависимости от того подан или нет уровень лог. «1» на соответствующий вход.

за период счёта (до 64) подсчитывается по формуле: N=32·x32+16·x16+8·x8+4·x4+2·x2+1·x1, где x1–x32 принимают значения соответственно 0 или 1 в зависимости от того подан или нет уровень лог. «1» на соответствующий вход.

6 Запоминающие устройства

6.1 Иерархия запоминающих устройств ЭВМ

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими устройствами. Микросхемы и системы памяти постоянно совершенствуются как в области схемотехнологии, так и в области развития новых архитектур.

Важнейшие параметры ЗУ находятся в противоречии. Так, например, большая информационная ёмкость не сочетается с высоким быстродействием, а быстродействие в свою очередь не сочетается с низкой стоимостью. Поэтому в ЗУ используется многоступенчатая иерархическая структура.

Читать дальше

за период счёта (до 64) подсчитывается по формуле: N=32·x32+16·x16+8·x8+4·x4+2·x2+1·x1, где x1–x32 принимают значения соответственно 0 или 1 в зависимости от того подан или нет уровень лог. «1» на соответствующий вход.

за период счёта (до 64) подсчитывается по формуле: N=32·x32+16·x16+8·x8+4·x4+2·x2+1·x1, где x1–x32 принимают значения соответственно 0 или 1 в зависимости от того подан или нет уровень лог. «1» на соответствующий вход.

![Стивен Хокинг - Черные дыры. Лекции BBC [litres]](/books/402420/stiven-hoking-chernye-dyry-lekcii-bbc-litres-thumb.webp)