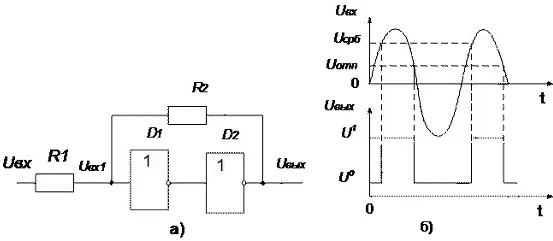

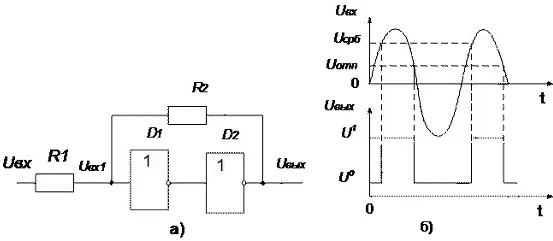

Несимметричный триггер может быть реализован на логических элементах. Для этого достаточно включить последовательно чётное число элементов НЕ и выход этой цепочки соединить со входом цепью обратной связи, образуемой резисторами R1 и R2 (Рисунок 53,а).

В отсутствие входного сигнала ( U вх =0) напряжение на выходе ( U вых =0). Если пренебречь входным током ЛЭ, то при U вх >0 напряжение на входе D1 U ВХ = U ВХ–R 1 I , где I =( U ВХ 1– U ВЫХ )/ R 2.

Таким образом,

U ВХ 1= U ВХ + ( U ВЫХ– U ВХ 1) R 1/ R 2 (5.3)

Рисунок 53 Триггер Шмита на логических элементах

С ростом U вх повышается напряжение U вх1, но пока U вх1 < U пор логические элементы остаются в исходном состоянии и на выходе сохраняется сигнал U 0. Когда U вх1 = U пор , происходит переключение логических элементов и на выходе возникает сигнал U ВЫХ=U ¹. В результате схема переходит в другое устойчивое состояние. Напряжение срабатывания можно определить из приведённого выше выражения (5.3), если принять U вх1=U пор , U ВЫХ=U ¹, U вх=U срб :

U СРБ= U ПОР + ( U ПОР – U 0) R 1/ R 2 (5.4)

Естественно, что при U вх1 > U срб на выходе схемы сохраняется состояние лог. «1».

При уменьшении U вх триггер переходит в исходное состояние, когда U вх=U отп . Значение U отп определяется из соотношения (5.3), если положить U вх1=U пор , U вых=U 1, U вх=U отп .

U ОТП= U ПОР + ( U 1– U ПОР ) R 1/ R 2 (5.5)

Из соотношений (5.4) и (5.5) следует, что U срб > U отп и, таким образом, амплитудная передаточная характеристика несимметричного триггера на ЛЭ имеет петлю гистерезиса. Вычитая (5.5) из (5.4), получаем

U СРБ – U ОТП = ( U 1– U 0) R 1/ R 2

Откуда видно, ширина петли гистерезиса пропорциональна логическому перепаду ∆ U Л .

Несимметричные триггеры применяют в качестве формирователей импульсов прямоугольной формы при воздействии на вход, например, синусоидального напряжения (Рисунок 53,б).

Поскольку выходное напряжение резко возрастает при U ВХ = U СРБ, то такие триггеры используют и в качестве компаратора напряжения — устройства, которое позволяет зафиксировать момент достижения сигналом некоторого заданного уровня.

Регистры — это функциональные узлы на основе триггеров, предназначенные для приёма, кратковременного хранения (на один или несколько циклов работы данного устройства), передачи и преобразования многоразрядной цифровой информации.

В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно — последовательные регистры.

5.2.1 Параллельные регистры (регистры памяти)

Запись кода в параллельные регистры осуществляется параллельным кодом, то есть во все разряды регистра одновременно. Их функция сводится только к приёму, хранению и передаче информации. В связи с этим параллельные регистры называют регистрами памяти.

Параллельный N-разрядный состоит из N триггеров, объединённых общими цепями управления.

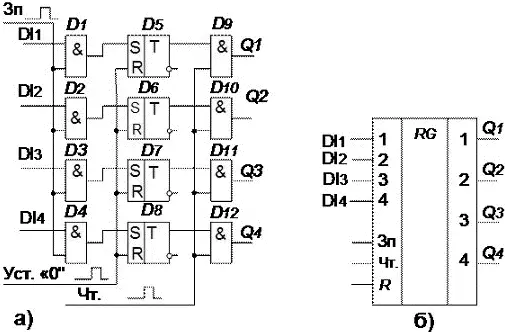

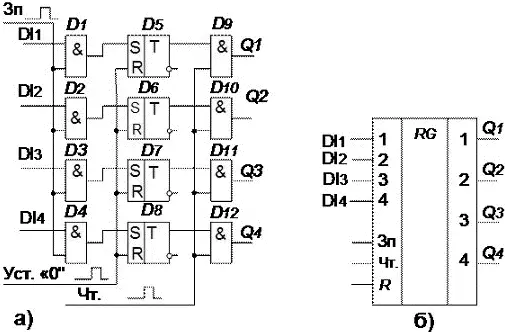

В качестве примера на рисунке 54,а приведена схема 4-разрядного параллельного регистра, построенного на RS-триггерах D5…D8. Элементы D1…D4 образуют цепь управления записью, а элементы D9…D12 — цепь управления чтением.

Рисунок 54 Функциональная схема а) и УГО б) параллельного регистра.

Перед записью информации все триггеры регистра устанавливают в состояние «0» путём подачи импульса «1» на их R-входы.

Записываемая информация подаётся на входы DI 1…DI 4. Для записи информации подаётся импульс «Зп», открывающий входные элементы «И». Код входного числа записывается в регистр. По окончании импульса «Зп» элементы D1…D4 закрываются, а информация, записанная в регистр, сохраняется несмотря на то, что входная информация может изменяться.

Для считывания информации подают сигнал «1» на вход «Чт». По этому сигналу на выходные шины регистра на время действия сигнала передаётся код числа, записанный в регистр. По окончанию операции чтения выходные ключи закрываются, а информация, записанная в регистр, сохраняется. То есть возможно многократное считывание информации. Условное графическое обозначение параллельного регистра приведено на рисунке 54,б.

Читать дальше

![Стивен Хокинг - Черные дыры. Лекции BBC [litres]](/books/402420/stiven-hoking-chernye-dyry-lekcii-bbc-litres-thumb.webp)