.ENTRY scramble;

scramble: I4=^input; {I4 присвоить адрес начала буфера входных данных}

I0=^output; {I0 присвоить адрес начала буфера выходных данных}

M4=1;

M0=mv; {M0=модификатор для реверса}

L4=0; {Линейные буферы}

L0=0;

ENA BIT_REV; {Разрешение инвертирования разрядов}

CNTR=N;

DO Met UNTIL СЕ; {Организация цикла}

AY1 =DM(I4,M4); {Чтение последовательно организованных данных}

Met: DM(I0,M0)=AY1; {Запись данных в ячейки в обратном порядке}

DIS BIT_REV; {Запрещение инвертирования разрядов}

RTS; {Возврат в вызывающую программу}

.ENDMOD;

В этой главе говорится об устройстве таймера сигнального процессора и его назначении.

Кроме рассмотренных нами вычислительных устройств, сигнальный процессор содержит в своем составе программируемый таймер, обеспечивающий автоматический отсчет времени, и два программируемых последовательных порта для связи с внешней периферией. Рассмотрим поочередно эти устройства.

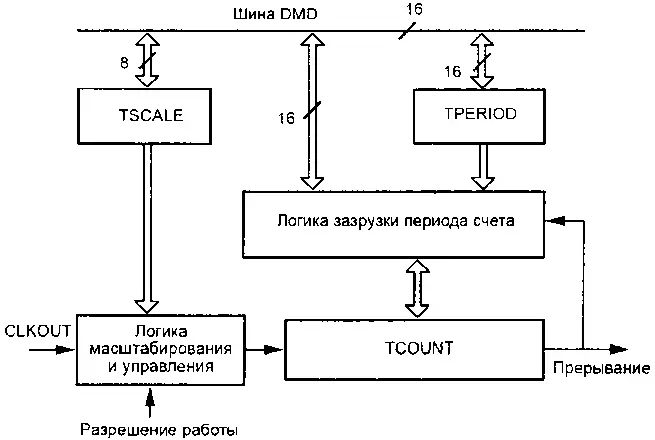

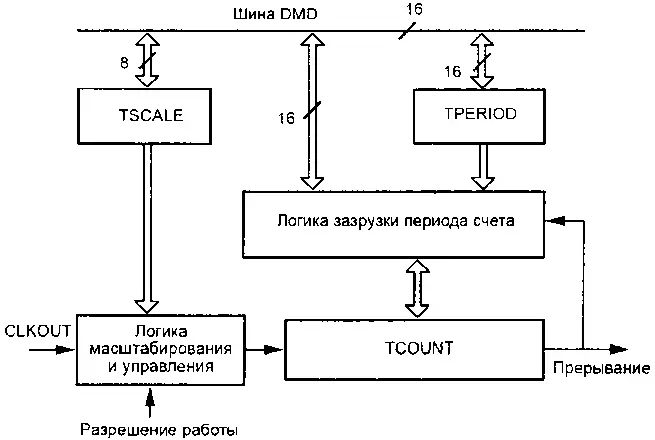

Программируемый таймер сигнального процессора позволяет циклически генерировать прерывания через определенные промежутки времени, кратные циклам процессора. Структурная схема таймера представлена на рис. 20.1.

Рис. 20.1. Структурная схема таймера

Как видно из рисунка, таймер включает в себя 16-разрядный регистр периода TPERIOD, 8-разрядный регистр масштабирования TSCALE, 16-разрядный регистр-счетчик TCOUNT и логику управления. Все три регистра отображены на область памяти данных процессора в соответствии с табл. 20.1.

Таблица 20.1 Формат регистров таймера, отображенных на память данных процессора

| Разряды регистров |

Адрес |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| TPERIOD |

0x3FFD |

| TCOUNT |

0x3FFC |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0x3FFB |

| Разряды регистров |

Адрес |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| TPERIOD |

0x3FFD |

| TCOUNT |

0x3FFC |

| TSCALE |

0x3FFB |

Разрешение работы таймера производится установкой в единицу 5-го разряда регистра состояния процессора MSTAT. Когда работа таймера разрешена, регистр-счетчик TCOUNT декрементируется сигналами от логики масштабирования. При достижении счетчиком нуля, формируется прерывание таймера для процессора. После чего в регистр-счетчик TCOUNT автоматически загружается значение регистра периода TPERIOD и работа таймера продолжается.

Регистр масштабирования TSCALE содержит коэффициент деления тактовой частоты процессора и позволяет изменять время между прерываниями таймера.

Значения регистров TPERIOD и TSCALE могут загружаться с шины DMD. Таким образом, с помощью таймера можно генерировать прерывания каждые (TPERIOD+1)*(TSCALE+1) циклов, т.е. от 1 до FFFFFF 16=16777215 10циклов. При тактовой частоте процессора 40МГц таймер может формировать прерывания с периодом от 20 нс до 0,3 с.

При необходимости прерывания таймера можно маскировать, сбрасывать или принудительно устанавливать программным образом.

Ниже приведен пример команд инициализации таймера:

{Регистр таймера TPERIOD=0x3FFD (Регистр периода)}

AX0=0X7FFF; DM(TPERIOD)=AX0;

{Регистр таймера TCOUNT=0x3FFC (Регистр счетчика)}

AX0=0X7FFF; DM(TCOUNT)=AX0;

{Регистр таймера TSCALE=0x3FFB (Регистр масштабирования)}

AX0=255; {ОТ 0 ДО 255} DM(TSCALE)=AX0;

Строка обработки прерывания в программе может иметь следующий вид:

jump V_TIMER; nop; nop; nop; {Вектор прерывания таймера}

Следующий пример обработчика прерывания таймера позволяет автоматически наращивать значения ячейки памяти 0x3000 и выводить эти значения в порт ввода-вывода по адресу 2000.

{===== Обработчик прерывания таймера =====}

V_TIMER:

ENA SEC_REG;

AX0=DM(0X3000);

AR=AX0 + 1;

DM(0X3000)=AR;

IO(2000)=AR;

RTI;

Подобным образом можно организовывать автоматическую регенерацию динамической памяти, подключаемой к сигнальному процессору. Учитывая, что объем такого типа памяти составляет десятки миллионов байт в одной микросхеме, можно догадаться о мощности устройств, создаваемых с ее применением. В то же время регенерация динамической памяти очень легко решается при подключении ее к сигнальному процессору.

Глава 21. Синхронные последовательные порты

В этой главе говорится о двух синхронных последовательных портах, входящих в состав сигнального процессора, об их устройстве, назначении и использовании.

Читать дальше