Любой из регистров MAC может быть прочитан и записан в одном цикле. Чтение данных происходит в начале цикла, а запись - в конце цикла. Прочитанное содержимое регистра в начале одного цикла записывается в конце предыдущего, следовательно, новое значение регистра может быть прочитано только в течение следующего цикла. Такой механизм позволяет входному порту предоставлять операнд для MAC в начале цикла и оперировать со следующим значением из памяти в конце того же цикла. Это относится и к выходному регистру.

Регистры MR, MF, MX, MY продублированы в теневых банках. Одновременно процессору может быть доступен лишь один из банков. Теневой банк регистров может быть активизирован для чрезвычайно быстрого контекстного переключения. Таким образом, новая задача, типа подпрограммы обработки прерывания, может выполняться без сохранения текущих данных в памяти, благодаря использованию теневых банков. Выбор первичного или теневого банка регистров определяется установкой нулевого разряда в регистре MSTAT состояний процессора. Если этот разряд установлен в 0, то выбран первичный банк.

Операции MAC

Теперь рассмотрим операции вычислительного устройства MAC, входные форматы данных, обработку переполнения и насыщения.

Набор стандартных операций MAC приведен в табл. 15.2.

Таблица 15.2 Набор стандартных операций MAC

| Операция |

Назначение |

| X*Y |

Умножение X на Y |

| MR+X*Y |

Умножение X на Y и сложение с MR |

| MR-X*Y |

Умножение X на Y и вычитание из MR |

| 0 |

Очистка MR |

Как было сказано выше, сигнальный процессор ADSP-2181 обеспечивает два режима работы операций умножения с накоплением. Первый из них — режим работы с дробными числами в формате 1.15. Второй — режим работы с целыми числами в формате 16.0.

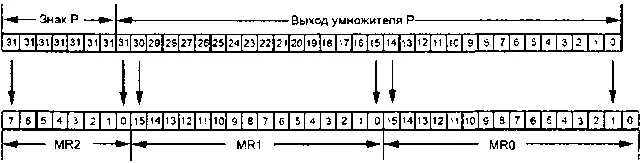

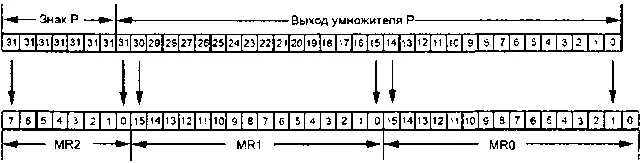

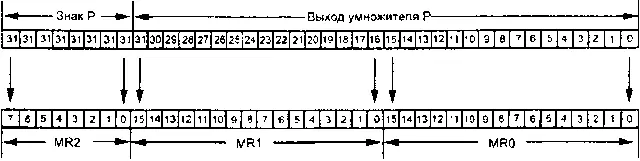

В дробном режиме выходной регистр P корректирует формат, т.е. прежде чем добавить значение в MR, оно сдвигается на один разряд влево. Таким образом, бит 31 регистра P запишется в 32-й разряд регистра MR, а 0-й разряд — в первый. В позицию младшего разряда (LSB) при этом записывается ноль. На рис. 15.2 показан дробный формат работы модуля умножения.

Рис. 15.2. Дробный формат работы модуля умножения

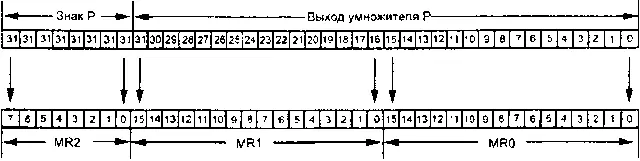

В целочисленном формате (рис. 15.3) регистр P не сдвигается, прежде чем прибавиться к MR.

Рис. 15.3. Целочисленный формат

Выбор режима осуществляется установкой 4-го разряда регистра MSTAT процессора. Если этот разряд установлен в 1, то выбран целочисленный режим. В любом формате блок умножения формирует 32-разрядный результат и передает его в блок сложения/вычитания, где получается конечное значение операции, которое записывается в MR.

Регистры ввода-вывода MAC

В операциях MAC обрабатываются данные, которые поступают на порты X и Y, а результат операций выводится на шину R. Ниже приведен перечень регистров, доступных для этих портов.

Регистры для входного порта X — MX0, МХ1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для входного порта Y — MY0, MY1, MF.

Регистры для выходного порта R — MR (MR0, MR1, MR2), MF.

Входные форматы данных

Для облегчения умножения входные операнды могут находиться в любых форматах. Входные форматы определяются как часть команды и выбираются динамически при обращении к блоку умножения.

Формат: «знаковый * знаковый» — используется при умножении двух знаковых чисел простой точности или двух старших частей знаковых чисел двойной точности.

Формат: «без знака * знаковый» или «знаковый * без знака» — используется при умножении верхней части знакового числа на нижнюю часть другого или для умножения знакового числа простой точности с числом той же точности без знака.

Формат: «без знака * без знака» — используется при умножении чисел простой точности без знака или нижних частей знаковых чисел двойной точности.

Операции над регистром MR

Как показано на рис. 15.1, регистр MR разбит на три регистра: MR0 (биты 0-15), MR1 (биты 16-31) и MR2 (биты 32-39). Каждый из этих регистров может быть загружен с DMD-шины и выведен на R-шину или DMD-шину. Регистр MR2 связан с младшими восемью разрядами этих шин. Во время передачи данных MR2 на R-шину или DMD-шину происходит добавление 8 знаковых разрядов для расширения числа до 16 разрядов. Кроме того, при загрузке данных с DMD-шины в регистр MR1 регистр MR2 служит как добавление регистра MR1, и заполняется значением старшего знакового разряда MR1. Для того чтобы загрузить в регистр MR2 данные, отличные от знакового разряда MR1, необходимо загружать MR2 после загрузки MR1. Загрузка регистра MR0 не влияет на регистры MR0 и MR1.

Читать дальше