В зависимости от назначения имеются платы ввода-вывода для цифрового ввода и вывода, аналогового ввода, аналогового ввода и вывода. В платах цифрового ввода-вывода применяются программируемые микросхемы параллельного ввода-вывода (см. гл. 7 ), а в платах аналогового ввода-вывода — аналого-цифровые (АЦП) и цифро-аналоговые (ЦАП) преобразователи.

Выпускаются также процессоры шины STE с последовательным интерфейсом RS-232C (см. гл. 8 ) для подключения к терминалу или внешнему главному микрокомпьютеру. Разработана плата шины STE для подключения к универсальной приборной шине IEEE-488 (см. гл. 8 ). Все это делает шину STE гибкой и универсальной.

Процессоры шины STE — это одноплатные компьютеры с ЦП, ПЗУ, ЗУПВ и интерфейсными схемами. На европлате размером 100x160 мм плотность монтажа оказывается очень высокой. Например, один из наиболее популярных процессоров состоит из более чем 30 микросхем, причем не менее четырех из них — в 40-контактных корпусах типа DIP.

Структурная схема типичного процессора шины STE показана на рис. 9.1 (сравните ее с конфигурациями из гл. 5 ).

Рис. 9.1. Структурная схема типичного процессора шины STE

Центральный процессор (ЦП) Z80 работает с частотой синхронизации 4 МГц. Системный генератор синхронизации, стабилизированный кварцем (см. гл. 5 ), функционирует с частотой 16 МГц. Затем с помощью делителя формируются сигналы синхронизации 8 МГц для контроллера динамического ЗУПВ, 4 МГц для ЦП и последовательного интерфейса RS-232C, 2 МГц для контроллера диска.

Системная синхронизация с частотой 16 МГц действует также на шине STE в целях использования ведомыми шины. Так как на шине в любой момент времени должен присутствовать только один сигнал синхронизации 16 МГц, а в системе может быть несколько процессорных плат, на печатной плате предусмотрена перемычка, запрещающая выход 16 МГц.

Контроллер динамического ЗУПВ формирует сигналы мультиплексных данных, а также сигналы выбора строки  и столбца

и столбца  для восьми микросхем динамических ЗУПВ с организацией 64КХ1 (см. гл. 6 ). Контроллер диска выполнен в виде одной БИС, а последовательный интерфейс реализован на базе программируемого контроллера последовательного интерфейса (см. гл. 7 ). В последовательном интерфейсе осуществляется сдвиг уровня для удовлетворения всех спецификаций интерфейса RS-232C (см. гл. 8 ).

для восьми микросхем динамических ЗУПВ с организацией 64КХ1 (см. гл. 6 ). Контроллер диска выполнен в виде одной БИС, а последовательный интерфейс реализован на базе программируемого контроллера последовательного интерфейса (см. гл. 7 ). В последовательном интерфейсе осуществляется сдвиг уровня для удовлетворения всех спецификаций интерфейса RS-232C (см. гл. 8 ).

Шины адреса и данных буферируются от шины STE с помощью двух 8-битных драйверов (шина адреса) и 8-битного приемника-передатчика (шина данных). Все эти микросхемы имеют тристабильные выходы (см. гл. 2 ), поэтому при необходимости их можно изолировать от внешней шины.

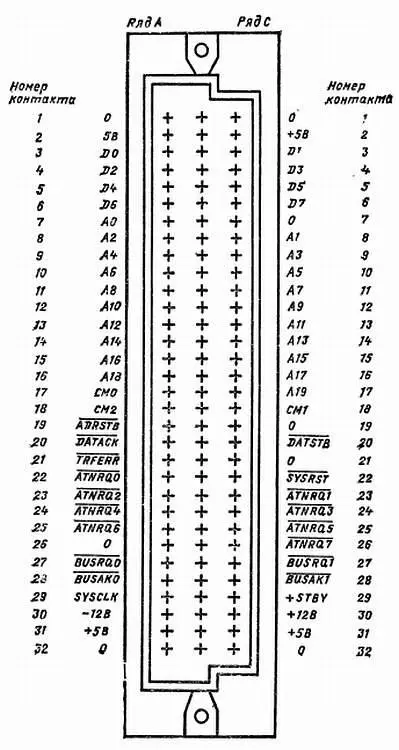

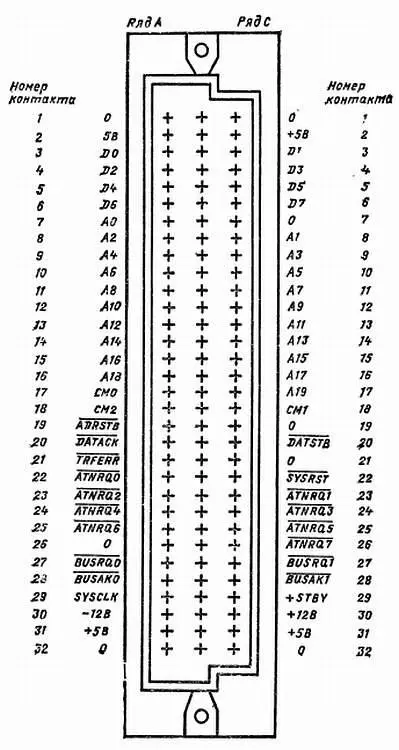

Разводка разъема шины STE приведена на рис. 9.2, где D0—D7 — линии данных; А0—А19 — линии адреса;  — строб адреса. Сигнал низкого уровня на этой линии показывает наличие на Шине действительного адреса;

— строб адреса. Сигнал низкого уровня на этой линии показывает наличие на Шине действительного адреса;  — строб данных.

— строб данных.

Рис. 9.2. Разводка контактов разъема шины STE

Сигнал низкого уровня на этой линии идентифицирует наличие на шине действительных данных; СМО — СМ2 — командные модификаторы, характеризующие тип цикла шины; — запрос шины. На этих линиях действуют сигналы низкого уровня, когда потенциальному ведущему шины необходимо получить доступ к ней;  линии подтверждения шины. Сигналы низкого уровня на этих линиях показывают, что запрос шины удовлетворен. Потенциальный ведущий шины может управлять шиной, если только он получил подтверждение на запрос шины;

линии подтверждения шины. Сигналы низкого уровня на этих линиях показывают, что запрос шины удовлетворен. Потенциальный ведущий шины может управлять шиной, если только он получил подтверждение на запрос шины;  — на эту линию квитирования выдает сигнал ведомый шины в цикле записи, показывая восприятие данных, или в цикле считывания, показывая действительность своих данных; TRFERR — ведомый шины выдает этот сигнал вместо при обнаружении ошибки;

— на эту линию квитирования выдает сигнал ведомый шины в цикле записи, показывая восприятие данных, или в цикле считывания, показывая действительность своих данных; TRFERR — ведомый шины выдает этот сигнал вместо при обнаружении ошибки;  — линия внимания запроса/прерывания (сигнал

— линия внимания запроса/прерывания (сигнал  имеет больший приоритет); SYSCLK — системная синхронизация 16 МГц;

имеет больший приоритет); SYSCLK — системная синхронизация 16 МГц;  — системный сброс.

— системный сброс.

Необходимо отметить, что линии командных модификаторов показывают операции считывания, записи ввода-вывода и памяти в соответствии с табл. 9.1.

Читать дальше

и столбца

и столбца  для восьми микросхем динамических ЗУПВ с организацией 64КХ1 (см. гл. 6 ). Контроллер диска выполнен в виде одной БИС, а последовательный интерфейс реализован на базе программируемого контроллера последовательного интерфейса (см. гл. 7 ). В последовательном интерфейсе осуществляется сдвиг уровня для удовлетворения всех спецификаций интерфейса RS-232C (см. гл. 8 ).

для восьми микросхем динамических ЗУПВ с организацией 64КХ1 (см. гл. 6 ). Контроллер диска выполнен в виде одной БИС, а последовательный интерфейс реализован на базе программируемого контроллера последовательного интерфейса (см. гл. 7 ). В последовательном интерфейсе осуществляется сдвиг уровня для удовлетворения всех спецификаций интерфейса RS-232C (см. гл. 8 ). — строб адреса. Сигнал низкого уровня на этой линии показывает наличие на Шине действительного адреса;

— строб адреса. Сигнал низкого уровня на этой линии показывает наличие на Шине действительного адреса;  — строб данных.

— строб данных.

линии подтверждения шины. Сигналы низкого уровня на этих линиях показывают, что запрос шины удовлетворен. Потенциальный ведущий шины может управлять шиной, если только он получил подтверждение на запрос шины;

линии подтверждения шины. Сигналы низкого уровня на этих линиях показывают, что запрос шины удовлетворен. Потенциальный ведущий шины может управлять шиной, если только он получил подтверждение на запрос шины;  — на эту линию квитирования выдает сигнал ведомый шины в цикле записи, показывая восприятие данных, или в цикле считывания, показывая действительность своих данных; TRFERR — ведомый шины выдает этот сигнал вместо при обнаружении ошибки;

— на эту линию квитирования выдает сигнал ведомый шины в цикле записи, показывая восприятие данных, или в цикле считывания, показывая действительность своих данных; TRFERR — ведомый шины выдает этот сигнал вместо при обнаружении ошибки;  — линия внимания запроса/прерывания (сигнал

— линия внимания запроса/прерывания (сигнал  имеет больший приоритет); SYSCLK — системная синхронизация 16 МГц;

имеет больший приоритет); SYSCLK — системная синхронизация 16 МГц;  — системный сброс.

— системный сброс.

![Крис Скиннер - Цифровой банк [Как создать цифровой банк или стать им] [litres]](/books/397315/kris-skinner-cifrovoj-bank-kak-sozdat-cifrovoj-b-thumb.webp)