При уменьшении U вх до уровня лог. «0» ( U вх = U 0), наоборот, транзистор VT1 закрыт, а транзистор VT2 находится в линейном режиме на границе с областью насыщения.

В схеме ЭСЛ (Рисунок 14,б) параллельно транзистору VT1 включается ещё один или несколько транзисторов (в зависимости от коэффициента объединения по входу), которые составляют одно из плеч переключателя тока. К выходам ЛЭ для повышения нагрузочной способности подключены два эмиттерных повторителя VT4 и VT5.

При подаче на все входы или на один из них, например, первый, сигнала U ВХ 1= U 1, транзистор VT1 открывается и через него протекает ток I 0, а транзистор VT3 закрывается.

U ВЫХ 1= U 1– U БЭ.нас = U 0

U ВЫХ 2= U ПИТ– U БЭ.нас = U 1

Таким образом, по первому выходу данная схема реализует логическую операцию ИЛИ-НЕ, а по второму — операцию ИЛИ. Нетрудно видеть, что пороговое напряжение U ПОР=U ОП , логический перепад Δ U = U 1- U 0= U БЭ.нас и помехоустойчивость схемы U + ПОМ = U - ПОМ =0,5 U БЭ.нас .

Входные токи элемента, а следовательно, и токи нагрузки ЭСЛ малы: I 0 ВХ ≈0, ток I 1 ВХ равен базовому току транзистора, работающего на границе области насыщения, а не в области насыщения. Поэтому нагрузочная способность элемента велика и коэффициент разветвления достигает 20 и более.

Поскольку логический перепад невелик, то нестабильность напряжения источника питания существенно влияет на помехоустойчивость ЭСЛ. Для повышения помехоустойчивости в схемах ЭСЛ заземляют не отрицательный полюс источника питания, а положительный. Это делается для того, чтобы большая доля напряжения помехи падала на большом сопротивлении R эи только малая её доля попадала на входы схемы.

При совместном использовании ЛЭ ЭСЛ и ТТЛ между ними приходится включать специальные микросхемы, которые согласуют уровни логических сигналов. Их называют преобразователями уровней (ПУ).

Высокое быстродействие ЭСЛ обусловлено следующими основными факторами:

1 Открытые транзисторы не находятся в насыщении, поэтому исключается этап рассасывания неосновных носителей в базах.

2 Управление входными транзисторами осуществляется от эмиттерных повторителей предшествующих элементов, которые, имея малое выходное сопротивление, обеспечивают большой базовый ток и, следовательно, малое время открывания и закрывания входных и опорного транзисторов.

3 Малый логический перепад сокращает до минимума время перезарядки паразитных емкостей элемента.

Все эти факторы в комплексе обеспечивают малое время фронта и среза выходного напряжения элементов ЭСЛ.

Для ЭСЛ характерны следующие средние параметры: U пит =–5В; U 1=–(0,7–0,9)В; U 0=–(1,5–2)В; tЗ Д.ср =3–7 нс; P пот =10–20 мВт.

Перспективными считаются серии К500 и К1500, причём серия К1500 относится к числу субнаносекундных и имеет время задержки распространения менее 1 нс. (Таблица 8).

Таблица 8 Параметры основных серий ЛЭ ЭСЛ

| Параметры |

Серии |

| К500 |

К1500 |

| Входной ток I 0 ВХ ,мА |

0,265 |

0,35 |

| Входной ток I 1 ВХ , мА |

0,0005 |

0,0005 |

| Выходное напряжение U 0 ВЫХ , В |

-1,85…-1,65 |

-1,81…-1,62 |

| Выходное напряжение U 1 ВЫХ , В |

-0,96…-0,81 |

-1,025…-0,88 |

| Выходное пороговое напряжение, В: |

| U 0 ВЫХ.пор |

-1,63 |

-1,61 |

| U 1 ВЫХ.пор |

-0,98 |

-1,035 |

| Время задержки распространения, нс |

2,9 |

1,5 |

| Допустимое напряжение помехи, В |

0,125 |

0,125 |

| Коэффициент разветвления K РАЗ |

15 |

— |

| Напряжение питания, В |

-5,2; -2,0 |

-4,5; -2,0 |

| Потребляемая мощность на элемент, мВт |

8…25 |

40 |

3.4 Транзисторная логика с непосредственными связями (ТЛНС)

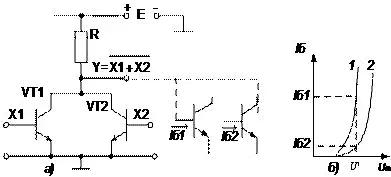

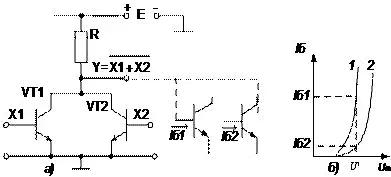

В схеме элемента ТЛНС сопротивление нагрузки включено в цепь соединенных коллекторов двух транзисторов (Рисунок 15,а). Входные сигналы X1 и X2 подаются на базы этих транзисторов. Если X1 и X2 одновременно равны «лог 0», то оба транзистора закрыты и на выходе схемы будет высокий потенциал Y=1. Если хотя бы на один, или на оба входа, подать высокий потенциал «лог 1», то один или оба транзистора открыты и на выходе схемы будет низкий потенциал Y=0. Таким образом, схема выполняет операцию ИЛИ-НЕ.

Рисунок 15 ЛЭ НСТЛ а) и входные характеристики транзисторов нагрузки б).

Читать дальше

![Стивен Хокинг - Черные дыры. Лекции BBC [litres]](/books/402420/stiven-hoking-chernye-dyry-lekcii-bbc-litres-thumb.webp)