** circuit file for profile: Bridgc1

*Libraries:

* Local Libraries :

.LIB ".\bridgcir.lib"

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

* Analysis directives:

.TRAN 0 400us 0 0.4us

.WCASE TRAN V( [4]) MAX OUTPUT ALL VARY DEV HI

.PROBE

WARNING Library file e:\spice\bridgcir.lib has changed since index file bridgcir.ind was created.

WARNING -- The timestamp changed from Sun Sep 05 21:51:14 1999 to Hon Sep 06 10:22:00 1999.

Making new index file bridgcir.ind for library file bridgcir.lib Index has 2 entries from 1 file(s).

**** BJT MODEL PARAMETERS

Q2H2222

NPN

IS 14.340000E-15

BF 255.9

**** Resistor MODEL PARAMETERS

Rbreak

R 1

SENSITIVITY NOMINAL

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 0.0000 ( 3) .7593 ( 4) 8.1468

( 5) 12.0000 ( 6) .1297

SENSITIVITY Q_Q1 Q2N2222 BF

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 0.0000 ( 3) .7593 ( 4) 8.1468

( 5) 12.0000 ( 6) .1297

SENSITIVITY R_RL RBREAK R

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 0.0000 ( 3) .7592 ( 4) 8.1454

( 5) 12.0000 ( 6) .1296

SORTED DEVIATIONS OF V(4) TEMPERATURE = 27.000 DEG С

SENSITIVITY SUMMARY

RUN MAXIMUM VALUE

NOMINAL 8.355 at T = 149.3200E-06

Q_Q1 Q2N2222 BF 8.355 at T = 149.3200E-06

( -4.2233E-03% change per 1% change in Model Parameter)

R_RL Rbreak R 8.3536 at T = 149.3200E-06

( -.169 % change per 1% change in Model Parameter)

WORST CASE ALL DEVICES

DEVICE MODEL PARAMETER NEW VALUE

Q_Q1 Q2N2222 BF 191.93 (Decreased)

R_RL Rbreak R .8 (Decreased)

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 0.0000 ( 3) .7870 ( 4) 8.4843

( 5) 12.0000 ( 6) .1532

**** SORTED DEVIATIONS OF V(4) TEMPERATURE = 27.000 DEG С

WORST CASE SUMMARY

RUN MAXIMUM VALUE

ALL DEVICES 8.6882 at T = 149.3200E-06

( 103.99% of Nominal)

NOMINAL 8.355 at T = 149.3200E-06

Рис. 17.31. Часть выходного файла для анализа на наихудший случай

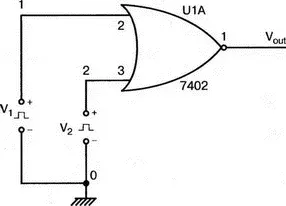

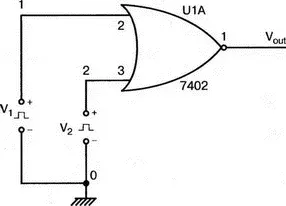

В Capture OrCAD имеется большой выбор цифровых устройств. Начнем новый проект с именем norgate и выберем Place, Part, перейдя к библиотеке eval. Начиная с компонентов 5550, 7400, 7401, …, вы увидите большой выбор цифровых компонентов, включая логические элементы И-НЕ, ИЛИ-НЕ, исключающее ИЛИ-инверторы, И-ИЛИ-инверторы, JK-триггеры, ведущие-ведомые триггеры, 2-разрядные двоичные полные сумматоры и другие. Все перечисленные устройства доступны в демонстрационной версии OrCAD.

В последнем примере главы 9 мы рассматривали логическую схему 7400: 2-входовую схему ИЛИ-НЕ. В качестве источников V 1и V 2были использованы источники напряжения типа PWL с выходным напряжением в виде последовательностей импульсов, представляющих уровни логических нулей и единиц. Эта схема может быть введена и в Capture OrCAD, как показано на рис. 17.32. Чтобы создать V 1и V 2, выберем компонент типа VPWL. Вспомним, как были описаны два источника в примере из главы 9:

V1 1 0 PWL(0s 0V 0.1ms 1V 1s 1V 1.0001S 0V

+ 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V 5s 1V)

V2 2 0 PWL((0s 0V 1.5s 0V 1.50001s 1V 2.5s 1V 2.50001s 0V

+ 3.5s 0V 3.50001s 1V 3.70001s 0V 5s 0V)

Рис. 17.32. Схема для исследования логического элемента И-НЕ

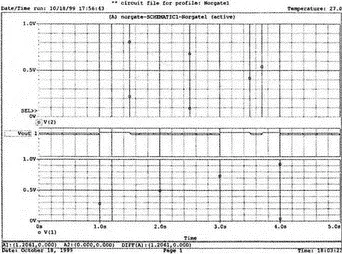

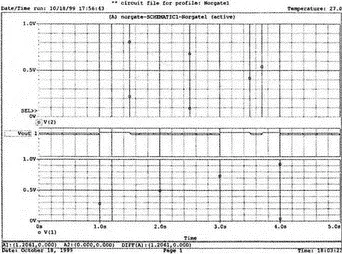

Войдя в Capture, дважды щелкните на компоненте V1 и в появившемся окне Property Editor введите следующие пары время-напряжение: «0s 0V 0.1ms 1V 1s 1V 1.0001s 0V 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V». Отметим, что в Capture можно ввести только 10 пар время-напряжение, в то время как в PSpice их число не ограничено. Дважды щелкните на компоненте V2 и введите следующие пары время-напряжение: «0s 0V 1,5s 0V 1,50001s 1V 2,5s 1V 2,50001s 0V 3,5s 0V 3,50001s 1V 3,7s 1V 3,70001s 0V 5s 0V». Завершите схему, выбрав Place, Net Alias для узлов 1, 2 и V out. Сохраните схему и подготовьте в PSpice новое моделирование с именем Norgate1. Выберите анализ переходных процессов на интервале t= 5 мс с максимальным размером шага в 1 мс. Проведите анализ и получите в Probe графики V(1) и Vout, a V(2) — на отдельном графике, как показано на рис. 17.33. Курсор на рисунке показывает, что при t =1,2 с, когда и V(1) и V(2) равны логическому нулю, выход V out равен логической единице. Уровни для обоих входных напряжений на этом графике совпадают с сеткой, что несколько затемняет картину.

Рис. 17.33. Диаграммы входных к выходного напряжений для элемента И-НЕ

Небольшая часть выходного файла показана на рис. 17.34. Интереснее всего проследить, как входные напряжения задаются в соответствующих командах. В состав этой схемы входят как аналоговые, так и цифровые схемы, аналоговые источники VPWL подключены к логическому элементу И-НЕ 7402. Это заставляет программу PSpice создавать набор аналого-цифровых интерфейсов, что вносит в простой проект излишние осложнения.

Читать дальше

Конец ознакомительного отрывка

Купить книгу