— они плохо подходят для моделирования процессоров с другой архитектурой. Иными словами, если вам нужна точность результатов, то микропроцессор, на котором построена эмулирующая система, должен быть максимально приближен к микропроцессору, который на этой системе моделируется;

— по разным причинам (скорость работы, стоимость, легкость подстройки) создатели эмуляторов вынуждены упрощать свои системы, что снижает точность результатов тестирования. Проще говоря, во время отладки «софтверного процессора» нет уверенности, что выполненный в железе прототип будет вести себя именно так — есть лишь некая, впрочем, довольно высокая вероятность, что его поведение будет примерно таким, как показала модель;

— многие инструменты для эмулирования работы процессоров либо дороги сами по себе, либо недешево обходятся при эксплуатации (в первую очередь из-за высокого энергопотребления).

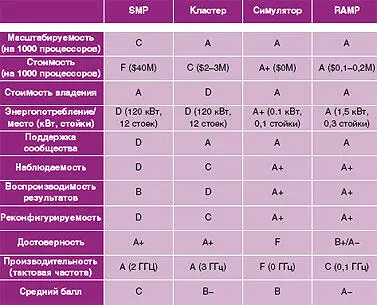

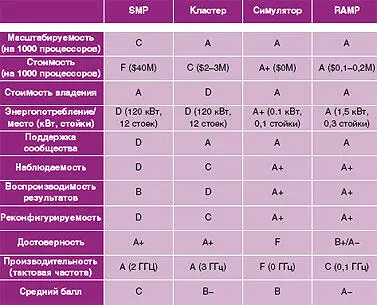

RAMP — не идеальное решение, не палочка-выручалочка, а такой же компромисс между стоимостью, скоростью, реконфигуриремостью и точностью, но многих из перечисленных недостатков почти лишен.

Эмуляторы против симуляторов

RAMP — это универсальный эмулятор, построенный на базе массива FPGA (матричная программируемая БИС). Такой подход объединяет в себе лучшее, что есть сегодня в эмуляции новых процессоров. С одной стороны, схема на перепрограммируемых БИС достаточно гибка, чтобы на ее базе можно было смоделировать любую известную параллельную архитектуру (не без ограничений, но о них чуть ниже). С другой — обладает достаточной производительностью, чтобы на RAMP можно было запускать операционные системы и приложения, проверяя работоспособность проектируемого процессора почти в реальных условиях (работать они будут в 10—20 раз медленнее, но и это очень приличный результат). Кроме того, он прекрасно масштабируется: на одной FPGA сегодня можно разместить порядка двадцати ядер (то есть на 1024-процессорную систему нужно от сорока до восьмидесяти FPGA), при этом скорость работы 1000-процессорной системы будет ненамного ниже, чем у 32-процессорной системы. Немаловажная для академических исследователей особенность — относительная дешевизна такого решения (железо для эмуляции 1000-ядерного процессора обойдется примерно в 100 тысяч долларов).

Но RAMP это не только железо, но и набор уже готовых моделей архитектур, описанных на специальном языке RDL (RAMP Description Language). В идеале исследовательское подразделение или факультет computer science, приобретая RAMP, вместе с небольшой кучкой железа, которую можно научить изображать другую кучку железа, получает почти все необходимые шаблоны. Вряд ли это очень важно для коммерческих разработчиков, а вот университетам очень пригодится.

Сегодня исследователи договорились о «портировании» на RAMP 32-битных процессоров IBM Power 405, Sun SPARC v8, Xilinx Microblaze (софт-процессор), 64-битного SPARC Niagara. Не исключено также создание моделей для 64-битного IBM Power и Tensilica, ARM, а также MIPS32 и MIPS64. Интеловских архитектур (x86, x86-64) на RAMP, видимо, не будет, хотя специалисты Intel в проекте участвуют.

Чтобы картина не получалась совсем уж радужной, упомянем и о недостатках RAMP, которые очевидны уже сегодня. Во-первых, FPGA-акселератор кое-где проигрывает софтверным симуляторам по функциональности, так как не умеет делать откаты (в случае софтверной симуляции можно отменить или пустить в обратном порядке любой набор инструкций), что, впрочем, компенсируется скоростью. Во-вторых, противники RAMP — а такие тоже есть — полагают, что заявления о точности эмуляции преждевременны, поскольку система в целом выглядит несбалансированной: быстрая память на медленных процессорах — не слишком стандартная конфигурация. Впрочем, Паттерсон к такой критике относится спокойно: по его словам, важна не относительная скорость выполнения тех или иных операций, а количество необходимых циклов процессора, а это — величина абсолютная. В-третьих, есть определенные физические ограничения, которые усложняют построение моделей процессорных архитектур. Так, например, затруднено построение эмуляторов современных процессоров с кэшем второго уровня емкостью больше 2 Мбайт, потому что объем памяти на борту стандартной FPGA меньше этого значения. Тем не менее недостающую память можно эмулировать отдельно. Кроме того, RAMP вполне работоспособен даже в том случае, когда построить полную RTL-модель не удается (например, ее просто нет — как нет модели Intel IA-32) или она слишком сложна для имплементации. В подобных ситуациях RAMP можно использовать в связке с софтверным симулятором, хотя результаты работы такого тандема и потребуют дополнительной верификации.

Читать дальше